STM32F405 Arm Cortex-M4 Microcontroller

The STM32F405xx family is based on the high-performance Arm Cortex-M4 32-bit RISC core that can operate at a frequency of up to 168 MHz; The Cortex-M4 core features a Floating Point Unit (FPU) which supports all Arm single-precision data-processing instructions and data types. The STM32F405 series also incorporates high-speed embedded memories (Flash memory up to 1 Mbyte, up to 192 Kbytes of SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals for seamless operation. All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, and a true random number generator (RNG). They also feature standard and advanced communication interfaces.

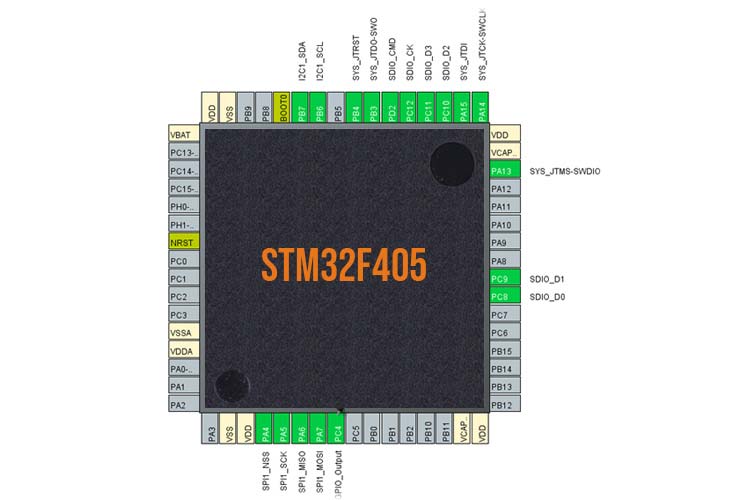

STM32F405 Pinout Configuration

|

Pin Num |

Pin Name |

Alternate functions |

Additional functions |

|

1 |

VBAT |

- |

- |

|

2 |

PC13 |

EVENTOUT |

RTC_OUT, RTC_TAMP1, RTC_TS |

|

3 |

PC14/OSC32_IN (PC14) |

EVENTOUT |

OSC32_IN |

|

4 |

PC15/ OSC32_OUT (PC15) |

EVENTOUT |

OSC32_OUT |

|

5 |

PH0/OSC_IN (PH0) |

EVENTOUT |

OSC_IN |

|

6 |

PH1/OSC_OUT (PH1) |

EVENTOUT |

OSC_OUT |

|

7 |

NRST |

- |

- |

|

8 |

PC0 |

OTG_HS_ULPI_STP/ EVENTOUT |

ADC123_IN10 |

|

9 |

PC1 |

ETH_MDC/ EVENTOUT |

ADC123_IN11 |

|

10 |

PC2 |

SPI2_MISO / OTG_HS_ULPI_DIR / ETH_MII_TXD2 /I2S2ext_SD/ EVENTOUT |

ADC123_IN12 |

|

11 |

PC3 |

SPI2_MOSI / I2S2_SD / OTG_HS_ULPI_NXT / ETH_MII_TX_CLK/ EVENTOUT |

ADC123_IN13 |

|

12 |

VSSA |

- |

- |

|

13 |

VDDA |

- |

- |

|

14 |

PA0/WKUP (PA0) |

USART2_CTS/ UART4_TX/ ETH_MII_CRS / TIM2_CH1_ETR/ TIM5_CH1 / TIM8_ETR/ EVENTOUT |

ADC123_IN0/WKU |

|

15 |

PA1 |

USART2_RTS / UART4_RX/ ETH_RMII_REF_CLK / ETH_MII_RX_CLK / TIM5_CH2 / TIM2_CH2/ EVENTOUT |

ADC123_IN1 |

|

16 |

PA2 |

USART2_TX/TIM5_CH3 / TIM9_CH1 / TIM2_CH3 / ETH_MDIO/ EVENTOUT |

ADC123_IN2 |

|

17 |

PA3 |

USART2_RX/TIM5_CH4 / TIM9_CH2 / TIM2_CH4 / OTG_HS_ULPI_D0 / ETH_MII_COL/ EVENTOUT |

ADC123_IN3 |

|

18 |

VSS |

- |

- |

|

19 |

VDD |

- |

- |

|

20 |

PA4 |

SPI1_NSS / SPI3_NSS / USART2_CK / DCMI_HSYNC / OTG_HS_SOF/ I2S3_WS/ EVENTOUT |

ADC12_IN4 /DAC_OUT1 |

|

21 |

PA5 |

SPI1_SCK/ OTG_HS_ULPI_CK / TIM2_CH1_ETR/ TIM8_CH1N/ EVENTOUT |

ADC12_IN5/DAC_ OUT2 |

|

22 |

PA6 |

SPI1_MISO / TIM8_BKIN/TIM13_CH1 / DCMI_PIXCLK / TIM3_CH1 / TIM1_BKIN/ EVENTOUT |

ADC12_IN6 |

|

23 |

PA7 |

SPI1_MOSI/ TIM8_CH1N / TIM14_CH1/TIM3_CH2/ ETH_MII_RX_DV / TIM1_CH1N / ETH_RMII_CRS_DV/ EVENTOUT |

ADC12_IN7 |

|

24 |

PC4 |

ETH_RMII_RX_D0 / ETH_MII_RX_D0/ EVENTOUT |

ADC12_IN14 |

|

25 |

PC5 |

ETH_RMII_RX_D1 / ETH_MII_RX_D1/ EVENTOUT |

ADC12_IN15 |

|

26 |

PB0 |

TIM3_CH3 / TIM8_CH2N/ OTG_HS_ULPI_D1/ ETH_MII_RXD2 / TIM1_CH2N/ EVENTOUT |

ADC12_IN8 |

|

27 |

PB1 |

TIM3_CH4 / TIM8_CH3N/ OTG_HS_ULPI_D2/ ETH_MII_RXD3 / TIM1_CH3N/ EVENTOUT |

ADC12_IN9 |

|

28 |

PB2/BOOT1 |

EVENTOUT |

- |

|

29 |

PB10 |

SPI2_SCK / I2S2_CK / I2C2_SCL/ USART3_TX / OTG_HS_ULPI_D3 / ETH_MII_RX_ER / TIM2_CH3/ EVENTOUT |

- |

|

30 |

PB11 |

I2C2_SDA/USART3_RX/ OTG_HS_ULPI_D4 / ETH_RMII_TX_EN/ ETH_MII_TX_EN / TIM2_CH4/ EVENTOUT |

- |

|

31 |

VCAP_1 |

- |

- |

|

32 |

VDD |

- |

- |

|

33 |

PB12 |

SPI2_NSS / I2S2_WS / I2C2_SMBA/ USART3_CK/ TIM1_BKIN / CAN2_RX / OTG_HS_ULPI_D5/ ETH_RMII_TXD0 / ETH_MII_TXD0/ OTG_HS_ID/ EVENTOUT |

- |

|

34 |

PB13 |

SPI2_SCK / I2S2_CK / USART3_CTS/ TIM1_CH1N /CAN2_TX / OTG_HS_ULPI_D6 / ETH_RMII_TXD1 / ETH_MII_TXD1/ EVENTOUT |

OTG_HS_VBUS |

|

35 |

PB14 |

SPI2_MISO/ TIM1_CH2N / TIM12_CH1 / OTG_HS_DM/ USART3_RTS / TIM8_CH2N/I2S2ext_SD/ EVENTOUT |

- |

|

36 |

PB15 |

SPI2_MOSI / I2S2_SD/ TIM1_CH3N / TIM8_CH3N / TIM12_CH2 / OTG_HS_DP/ EVENTOUT |

RTC_REFIN |

|

37 |

PC6 |

I2S2_MCK / TIM8_CH1/SDIO_D6 / USART6_TX / DCMI_D0/TIM3_CH1/ EVENTOUT |

- |

|

38 |

PC7 |

I2S3_MCK / TIM8_CH2/SDIO_D7 / USART6_RX / DCMI_D1/TIM3_CH2/ EVENTOUT |

- |

|

39 |

PC8 |

TIM8_CH3/SDIO_D0 /TIM3_CH3/ USART6_CK / DCMI_D2/ EVENTOUT |

- |

|

40 |

PC9 |

I2S_CKIN/ MCO2 / TIM8_CH4/SDIO_D1 / /I2C3_SDA / DCMI_D3 / TIM3_CH4/ EVENTOUT |

- |

|

41 |

PA8 |

MCO1 / USART1_CK/ TIM1_CH1/ I2C3_SCL/ OTG_FS_SOF/ EVENTOUT |

- |

|

42 |

PA9 |

USART1_TX/ TIM1_CH2 / I2C3_SMBA / DCMI_D0/ EVENTOUT |

OTG_FS_VBUS |

|

43 |

PA10 |

USART1_RX/ TIM1_CH3/ OTG_FS_ID/DCMI_D1/ EVENTOUT |

- |

|

44 |

PA10 |

USART1_CTS / CAN1_RX / TIM1_CH4 / OTG_FS_DM/ EVENTOUT |

- |

|

45 |

PA12 |

USART1_RTS / CAN1_TX/ TIM1_ETR/ OTG_FS_DP/ EVENTOUT |

- |

|

46 |

PA13 |

JTMS-SWDIO/ EVENTOUT |

- |

|

47 |

VCAP_2 |

- |

- |

|

48 |

VDD |

- |

- |

|

49 |

PA14 |

JTCK-SWCLK/ EVENTOUT |

- |

|

50 |

PA15 |

JTDI/ SPI3_NSS/ I2S3_WS/TIM2_CH1_ETR / SPI1_NSS / EVENTOUT |

- |

|

51 |

PC10 |

SPI3_SCK / I2S3_CK/ UART4_TX/SDIO_D2 / DCMI_D8 / USART3_TX/ EVENTOUT |

- |

|

52 |

PC11 |

UART4_RX/ SPI3_MISO / SDIO_D3 / DCMI_D4/USART3_RX / I2S3ext_SD/ EVENTOUT |

- |

|

53 |

PC12 |

UART5_TX/SDIO_CK / DCMI_D9 / SPI3_MOSI /I2S3_SD / USART3_CK/ EVENTOUT |

- |

|

54 |

PD2 |

TIM3_ETR/UART5_RX/ SDIO_CMD / DCMI_D11/ EVENTOUT |

- |

|

55 |

PB3 |

JTDO/ TRACESWO/ SPI3_SCK / I2S3_CK / TIM2_CH2 / SPI1_SCK/ EVENTOUT |

- |

|

56 |

PB4 |

NJTRST/ SPI3_MISO / TIM3_CH1 / SPI1_MISO / I2S3ext_SD/ EVENTOUT |

- |

|

57 |

PB5 |

I2C1_SMBA/ CAN2_RX / OTG_HS_ULPI_D7 / ETH_PPS_OUT/TIM3_CH2 / SPI1_MOSI/ SPI3_MOSI / DCMI_D10 / I2S3_SD/ EVENTOUT |

- |

|

58 |

PB6 |

I2C1_SCL/ TIM4_CH1 / CAN2_TX / DCMI_D5/USART1_TX/ EVENTOUT |

- |

|

59 |

PB7 |

I2C1_SDA / FSMC_NL / DCMI_VSYNC / USART1_RX/ TIM4_CH2/ EVENTOUT |

- |

|

60 |

BOOT0 |

- |

VPP |

|

61 |

PB8 |

TIM4_CH3/SDIO_D4/ TIM10_CH1 / DCMI_D6 / ETH_MII_TXD3 / I2C1_SCL/ CAN1_RX/ EVENTOUT |

|

|

62 |

PB9 |

SPI2_NSS/ I2S2_WS / TIM4_CH4/ TIM11_CH1/ SDIO_D5 / DCMI_D7 / I2C1_SDA / CAN1_TX/ EVENTOUT |

- |

|

63 |

VSS |

- |

- |

|

64 |

VDD |

- |

- |

Features and Specifications

- Arm 32-bit Cortex-M4 CPU with FPU, Adaptive real-time accelerator (ART Accelerator)

- Max Operating Voltage 1.8 - 3.6V

- Up to 1 Mbyte of Flash memory with Up to 192+4 Kbytes of SRAM

- LCD parallel interface, 8080/6800 modes

- Serial wire debug (SWD) & JTAG

- 4-to-26 MHz crystal oscillator

- Internal 16 MHz factory-trimmed RC (1% accuracy)

- 32 kHz oscillator for RTC with calibration

- 3×12-bit, 2.4 MSPS A/D converters: up to 24 channels

- 2×12-bit D/A converters

- General-purpose DMA: 16-stream DMA controller with FIFOs and burst support

- USB 2.0 full-speed device/host/OTG controller with on-chip PHY

- 10/100 Ethernet MAC with dedicated DMA: supports IEEE 1588v2 hardware, MII/RMII

- True random number generator

- CRC calculation unit

- 96-bit unique ID

- Junction temperature: –40 to + 125 °C

Note: Complete technical information can be found in the STM32F405 Datasheet, given at the bottom of this page.

Other STM32 ICS

STM32F030C6, STM32F030C8, STM32F030CC, STM32F103C8T6, STM32 Nucleo

How to Use the STM32F405 IC

The STM32F405 series microcontrollers are some of the most popular microcontrollers out there and can be used in a wide variety of applications. Other than that, the forum of STMicroelectronics is very huge and full of resources. This family of microcontrollers from STMicroelectronics is based on the ARM Cortex-M 32-bit processor core. The STM32 microcontrollers offer a large number of serial and parallel communication peripherals that can be used to interface with different electronic devices like sensors, displays, cameras, motors, etc. All STM32 variants come with internal Flash memory and RAM.

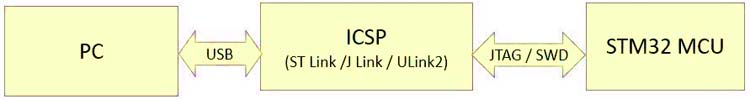

As it's a very popular microcontroller, development tools are pretty easy to get, though there are many development tools available, the most popular ones are ICSP, JTAG, and SWD.

In terms of software tools compilers and debuggers, there are a few but the most popular ones are Keil MDK ARM (uVison5 IDE) and CoIDE that can be used to write and compile the code. Once the code and compilation is done Keil U-Link 2, Segger J-Link, or ST-Link programmers can be used to upload the code to the microcontroller

Applications

The STM32 MCUs are commonly used in many industrial and commercial products these days. Some specific applications include-

- Low Power portable Electronics

- Robotics

- System Automation

- Rapid prototyping

- CRC calculations

- Consumer products

- Drone controllers

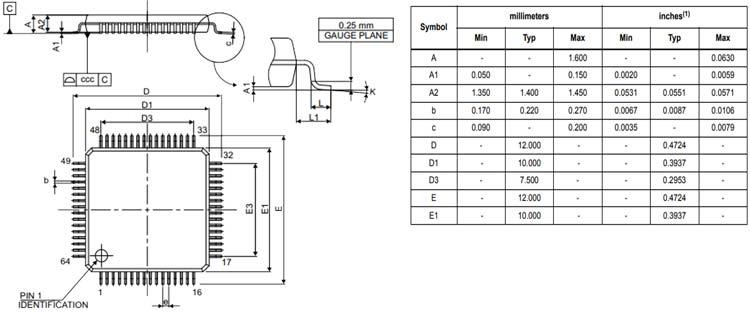

2D Model and Dimensions

If you are looking to include this IC for your next PCB project, this 2D model of the device will come in handy.