# Advanced 644 x 604 pixel, backside illuminated global shutter, ultra compact sensor, with high QE, high MTF, excellent PLS, and full-features

| Order code    | Description |

|---------------|-------------|

| VD55G0CCA1/RW | Bare die    |

#### **Application**

Engineered for high-performance computer vision applications, including AR/VR, personal and industrial robotics, drones, barcodes, biometrics and gestures, embedded vision or scene recognition.

Typical use cases where highperformance near IR sensing is key. Demanding computer vision on scene with movement requiring no shutter artifacts.

#### **Features**

- Global shutter technology, STMicroelectronics proprietary single layer

- 3D stacked sensor 40 nm/65 nm

- 2.61 μm x 2.61 μm BSI pixel with full CDTI (capacitive deep trench)

- High performance with excellent

- QE (quantum efficiency)

- MTF (modulation transfer function) up to near IR

- Perfect PLS (shutter efficiency)

- Smallest sensor on market with:

- Compact die size: 2.6 mm x 2.5 mm

- 640 pixel x 600 pixel resolution

- Very small pixel array, 1.67 mm x 1.57 mm

- Optical format between 1/9 inch

- Operating junction temperature: -30°C to 85°C

- Single lane transmitter MIPI CSI-2 (copyright© 2005-2010 MIPI Alliance, Inc. Standard for camera serial interface 2 (CSI-2) version 1.0) version 1.3, 1.2 Gbps per lane

- Fast mode+ I<sup>2</sup>C control interface

- Integrated temperature sensor

- Up to 210 fps (frames per second) at full resolution and 260 fps with VGA resolution

- Programmable sequences of 4-frame contexts, including frame parameters

- Automatic dark calibration

- Dynamic defective correction

- · Embedded auto-exposure

- 4 multiple function IO, dynamically programmable with frame contexts (GPIO, strobe pulse, pulse-width modulation, V sync)

- Up to 4 illumination control outputs, synchronized with sensor integration periods and leader or follower external frame start

- Mirror/flip readout

- Fully sequenceable with frame contexts

- Crop

- Binning (x2 and x4)

- Analog binning: 320x240 @ 500 fps, 320x252 @ 480 fps, 320x300 @ 414 fps

- Subsampling (x2 and x4)

### **Description**

The VD55G0 is a global shutter image sensor with high BSI performance which captures up to 210 frames per second in a 644 x 604 resolution format. The pixel construction of this device minimizes crosstalk while enabling a high quantum efficiency (QE) in the near infrared spectrum.

## Acronyms and abbreviations

Table 1. Acronyms and abbreviations

| Acronym/abbreviation | Definition                          |  |

|----------------------|-------------------------------------|--|

| BSI                  | backside illumination               |  |

| CCI                  | camera control interface            |  |

| CP                   | charge pump                         |  |

| CPU                  | central processing unit             |  |

| CRA                  | chief ray angle                     |  |

| CSI                  | camera serial interface             |  |

| DTI                  | deep trend isolation                |  |

| EMI                  | electromagnetic interference        |  |

| EMC                  | electromagnetic compatibility       |  |

| EXTCLK               | external clock                      |  |

| FoV                  | field of view                       |  |

| FPN                  | fixed pattern noise                 |  |

| fps                  | frames per second                   |  |

| GPIO                 | general-purpose input/output        |  |

| I <sup>2</sup> C     | inter-integrated circuit (bus)      |  |

| IP                   | intellectual property               |  |

| ISL                  | intelligent status line             |  |

| ISP                  | image signal processor              |  |

| LDO                  | low dropout regulator               |  |

| LP                   | low power                           |  |

| MIPI                 | mobile industry processor interface |  |

| OIF                  | output interface                    |  |

| OTP                  | one-time programmable               |  |

| QE                   | quantum efficiency                  |  |

| PHY                  | physical layer                      |  |

| PLS                  | photo light sensitivity             |  |

| PWM                  | pulse-width modulation              |  |

| STBY                 | standby                             |  |

| SW                   | software                            |  |

DS13170 - Rev 10 page 2/30

## 2 Overview

**Table 2. Technical specifications**

| Feature           |                                | Detail                                                 |  |

|-------------------|--------------------------------|--------------------------------------------------------|--|

| Pixel re          | Pixel resolution               |                                                        |  |

| Sensor te         | echnology                      | 3D stacked                                             |  |

| Pixel             | size                           | 2.61 µm x 2.61 µm                                      |  |

| Analo             | g gain                         | x1–x8                                                  |  |

|                   | 60 fps                         | 55 mW                                                  |  |

| Power consumption | 30 fps                         | 35 mW                                                  |  |

|                   | 10 fps                         | 14 mW                                                  |  |

| Junction temper   | rature range (Tj)              | -30°C to 85°C functional                               |  |

| Shu               | Shutter                        |                                                        |  |

| Packag            | Package option                 |                                                        |  |

| Frame rate at     | Frame rate at full resolution  |                                                        |  |

| CSI-2 serial into | erface data rate               | Up to 1.2 Gbps                                         |  |

| Pixel outp        | out format                     | RAW10 and RAW8                                         |  |

|                   |                                | 2.8 V analog supply                                    |  |

| Supply            | voltages                       | 1.8 V digital – IO supply                              |  |

|                   |                                | 1.15 V digital – core supply                           |  |

| Temperature se    | Temperature sensor accuracy    |                                                        |  |

| External clock f  | External clock frequency range |                                                        |  |

| Frame sync        | chronization                   | Internal, external I <sup>2</sup> C, external hardware |  |

DS13170 - Rev 10 page 3/30

### 3 Functional description

### 3.1 Interfaces

### 3.1.1 Inter-integrated circuit (I<sup>2</sup>C)

The VD55G0 is configured and controlled via an I<sup>2</sup>C interface. It operates in either Fast mode (up to 400 kHz) or Fast+ mode (up to 1 MHz) at 1.8 V. After the CPU boot sequence, the default I<sup>2</sup>C configuration is fast mode plus with a sink capability set to 20 mA. Drive capability can be decreased to 4 mA (fast mode) by writing a dedicated register once the system has booted.

Device addressing uses a CCI protocol with 2-byte subaddresses.

The default sensor address, 0x20 (including R/W bit), can be overridden:

- Permanently if a non-null value is stored in the OTP dedicated register

- Dynamically with a CPU command when the CPU state is SW STBY

#### 3.1.2 Camera serial interface (CSI)

The sensor is ready to connect via a single lane mobile industry processor interface (MIPI) CSI-2 serial interface. The single lane MIPI CSI-2 serial interface supports up to 1.2 Gbps. Resolution is scalable between RAW8 and RAW10.

### 3.2 Power supplies

The power supplies required by the sensor are:

- 2.8 V for the analog blocks

- 1.8 V for the digital I/Os

- 1.15 V for the core digital logic and MIPI CSI-2 output drivers

The pixel array requires different positive and negative voltages, all internally generated by charge pumps and regulators. Two voltage references, internally generated, need external decoupling capacitors.

The internal CPU handles the entire power management of the sensor to guarantee the lowest power consumption at any given time.

#### 3.3 Clock

An input clock is required from an external digital clock source in the range of 6 MHz to 27 MHz.

DS13170 - Rev 10 page 4/30

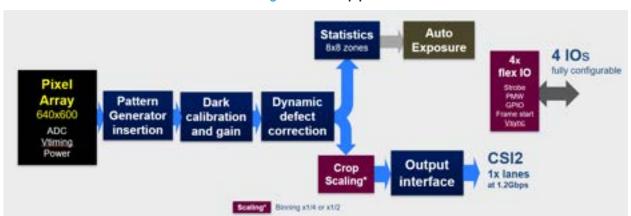

### 3.4 Video pipe

The video pipe performs a number of functions designed to ensure an image of high quality. These functions include:

- Analog subsampling

- Pattern generation

- Defective pixel correction

- Dark calibration

- Auto exposure

- Digital binning

- Embedded status lines

- Output interface

- Context

- Crop

Figure 1. Video pipe

DS13170 - Rev 10 page 5/30

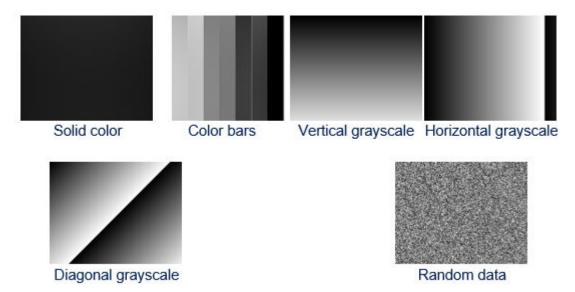

### 3.4.1 Pattern generation

The pattern generation allows the insertion of digital patterns in the frame. Two modes are available:

- Whole or part of the active data is replaced with a pattern

- · Dark lines are kept untouched

The available patterns are:

- Solid color

- Color bars

- Vertical grayscale

- · Horizontal grayscale

- Diagonal grayscale

- Random data

Figure 2. Available patterns

### 3.4.2 Defective pixel correction

Active pixels are automatically corrected by a dynamic algorithm embedded in the sensor ISP. This mechanism can be deactivated for specific use cases such as structured light.

#### 3.4.3 Dark calibration

A dark calibration is performed to extract the dark rows from the stream. Then, the dark noise level computed by this block is averaged and removed from the pixels in the active image.

A temporal smoothing and a sub bit dithering is applied to avoid a sudden one-code step.

Dark calibration implements a digital gain feature with a granularity of 1/256.

### 3.4.4 Auto exposure

The sensor integrates an auto exposure module to compute statistics on a given part of the active image. This module allows the exposure parameter to be changed accordingly.

### 3.4.5 Digital binning

The digital binning process reduces the image resolution by a factor of 2 or 4 in each direction. Digital binning is weighted to avoid special phase shift, an artifact which may occur on the output image.

DS13170 - Rev 10 page 6/30

### 3.4.6 Embedded status lines

The output interface (OIF) embeds the intelligent status line generator (ISLGEN) IP. This allows the metadata to be sent through the MIPI image data interface. Optionally, these data lines can be deactivated.

### 3.4.7 Output interface (OIF)

The OIF embeds a single data lane MIPI D-PHY interface. It supports up to 1.2 Gb/s of data. RAW10 and RAW8 data formats are supported over the CSI2-OIF.

The OIF can output a combination of the following:

- Intelligent status lines

- Frame data

#### 3.4.8 Context

The sensor allows the configuration of up to four different rolling contexts. Contexts can be chained one to another in an ending or non-ending sequence.

### 3.4.9 Subsampling

The device supports x2 and x4 subsampling, which reduces overall image size and keeps the same field of view (FoV). Subsampling is applied vertically and horizontally during the ADC readout, where every two or every four pixels are read. When subsampling is used, the frame rate can be increased by decreasing the frame length. Digital binning and subsampling are mutually exclusive.

### 3.4.10 Crop

The host can accurately choose which area of the whole pixel array it receives. This reduces traffic on the CSI interface and saves processing time.

### 3.5 Synchronization modes

The sensor has multiple synchronization modes:

- 1. Leader mode

- 2. Follower mode:

- a. Using GPIO pulses

- b. Using I2C triggering commands

DS13170 - Rev 10 page 7/30

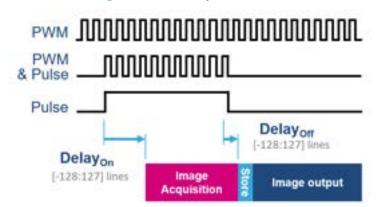

### 3.6 General purpose input/outputs (GPIOs)

The sensor provides four GPIOs:

- GPIO0 is used as a frame start synchronization signal or as a generic GPIO if not used for this function

- GPIO[1-3] are used as strobe output, PWM output, VSYNC or as a generic GPIO as per the configuration

PWM

Pulse

Vsync

GPIO

0 to 3

Frame

Start\*

\*Only for GPIO 0

Figure 3. GPIO modes

All GPIO settings are fully configurable for the four context setups. Each output signal can be mapped to one or several of the GPIOs. All GPIOs have configurable polarity.

Figure 4. PWM and pulse overview

DS13170 - Rev 10 page 8/30

### 3.7 Use cases

Table 3. Functional use cases

| Resolution      | ADC resolution |         |  |  |

|-----------------|----------------|---------|--|--|

| Resolution      | 9 bit          | 10 bit  |  |  |

| 644 x 604       | 210 fps        | 185 fps |  |  |

| 640 x 560       | 225 fps        | 205 fps |  |  |

| VGA 640 x 480   | 260 fps        | 225 fps |  |  |

| QVGA 320 x 240  | 430 fps        | 390 fps |  |  |

| QQVGA 160 x 120 | 760 fps        | 600 fps |  |  |

| 128 x 128       | 640 fps        | 580 fps |  |  |

This global shutter pixel has full deep trend isolation (DTI) for ultra-low crosstalk, and high sensitivity. VD55G0 product is designed to work in combination with a module/package with near infrared bandpass filter. For a use in monochromatic mode (no IR filter, visible domain), electrical performances are tested. For image quality performance, it is recommended the end users validate their own module and package performance (lens, FoV...).

DS13170 - Rev 10 page 9/30

## 4 Pin description and assignment

Table 4. Pin description table

| Ball name      | Туре        | Description                                  | Reset state | Reference supply |  |

|----------------|-------------|----------------------------------------------|-------------|------------------|--|

|                |             | Power supply                                 |             |                  |  |

| VCORE          |             | 1.15 power supply for the digital core       |             | 1.15 V           |  |

| VDDIO          |             | 1.8 V power supply for the digital core      |             | 1.8 V            |  |

| VANA           | PWR         | 2.8 V power supply for the digital core      |             | 2.8 V            |  |

| DGND           |             | Digital ground                               |             | VDDIO            |  |

| AGND           |             | Analog ground                                |             | VANA             |  |

|                |             | Reference                                    |             |                  |  |

| RCALIB         |             | Not connected                                |             | VCORE            |  |

| VCPNEG_IN      |             | Must be connected to VCPNEG_OUT              |             |                  |  |

| VCPNEG_OUT     | REF         | Must be connected to VCPNEG_IN               |             | VANA             |  |

| VCPPOS_IN      |             | Must be connected to VCPPOS_OUT              |             | VAIVA            |  |

| VCCPOS_OUT     |             | Must be connected to VCPPOS_IN               |             |                  |  |

|                |             | CSI-2 interface                              |             |                  |  |

| DATA1P, DATA1N | MIPI DPHY   | CSI-2 data lane 1, positive and negative     |             | VCORE            |  |

| CLKP, CLKN     | WIIFT DETTI | CSI-2 clock, positive and negative           | Low         | VCORE            |  |

|                |             | Host interface                               |             |                  |  |

| XSHUTDOWN      | I           | Reset active low                             |             |                  |  |

| SDA            | Ю           | I²C data                                     |             |                  |  |

| SCL            | I           | I <sup>2</sup> C clock                       |             |                  |  |

| GPIO0          |             |                                              |             | VDDIO            |  |

| GPIO1          | IO          | Conoral numero I/O and straho light control  | Low         | VDDIO            |  |

| GPIO2          | 10          | General purpose I/O and strobe light control | LOW         |                  |  |

| GPIO3          |             |                                              |             |                  |  |

| CLKIN          | I           | Input clock                                  |             |                  |  |

|                |             | Other pins                                   |             |                  |  |

| PORTEST        | I           | Must be connected to digital ground          |             | VDDIO            |  |

| NC             |             | Not connected                                |             |                  |  |

DS13170 - Rev 10 page 10/30

Table 5. Pin coordinates

The pin coordinates (0, 0) are the die center

| Pin number | Bonding point X coordinate | Bonding point Y coordinate | Net name  |

|------------|----------------------------|----------------------------|-----------|

| 1          | -1087.46                   | 1144.4                     | DGND      |

| 2          | -928.04                    | 1144.4                     | VANA      |

| 3          | -824.49                    | 1144.4                     | AGND      |

| 4          | -720.94                    | 1144.4                     | VCORE     |

| 5          | -617.39                    | 1144.4                     | VCORE     |

| 6          | -513.84                    | 1144.4                     | DGND      |

| 7          | -410.29                    | 1144.4                     | VANA      |

| 8          | -306.74                    | 1144.4                     | AGND      |

| 9          | -203.19                    | 1144.4                     | VANA      |

| 10         | -99.64                     | 1144.4                     | AGND      |

| 11         | 3.91                       | 1144.4                     | VANA      |

| 12         | 107.46                     | 1144.4                     | AGND      |

| 13         | 211.01                     | 1144.4                     | DGND      |

| 14         | 314.56                     | 1144.4                     | DGND      |

| 15         | 418.11                     | 1144.4                     | VCORE     |

| 16         | 595.08                     | 1144.4                     | NC        |

| 17         | 698.63                     | 1144.4                     | VDDIO     |

| 18         | 802.18                     | 1144.4                     | PORTST    |

| 19         | 905.73                     | 1144.4                     | NC        |

| 20         | 1076.96                    | 1144.4                     | VCORE     |

| 21         | 1184.9                     | 1045.38                    | SCL       |

| 22         | 1184.9                     | 895.32                     | SDA       |

| 23         | 1184.9                     | 772.31                     | DGND      |

| 24         | 1184.9                     | 668.74                     | XSHUTDOWN |

| 25         | 1184.9                     | 565.16                     | VANA      |

| 26         | 1184.9                     | 461.6                      | GPIO3     |

| 27         | 1184.9                     | 358.03                     | DGND      |

| 28         | 1184.9                     | 254.45                     | GPIO2     |

| 29         | 1184.9                     | 150.88                     | GPIO1     |

| 30         | 1184.9                     | 47.31                      | VCORE     |

| 31         | 1184.9                     | -56.25                     | VDDIO     |

| 32         | 1184.9                     | -159.83                    | DGND      |

| 33         | 1184.9                     | -263.39                    | VCORE     |

| 34         | 1184.9                     | -366.97                    | GPIO0     |

| 35         | 1184.9                     | -470.54                    | DGND      |

| 36         | 1184.9                     | -574.11                    | VCORE     |

| 37         | 1184.9                     | -677.68                    | CLKIN     |

| 38         | 1184.9                     | -781.25                    | DGND      |

| 39         | 1184.9                     | -884.82                    | DGND      |

| 40         | 1184.9                     | -1034.88                   | AGND      |

DS13170 - Rev 10 page 11/30

| Pin number | Bonding point X coordinate | Bonding point Y coordinate | Net name  |

|------------|----------------------------|----------------------------|-----------|

| 41         | 1087.46                    | -1144.4                    | VANA      |

| 42         | 937.38                     | -1144.4                    | VDDIO     |

| 43         | 833.82                     | -1144.4                    | VCORE     |

| 44         | 730.25                     | -1144.4                    | CLKN      |

| 45         | 626.68                     | -1144.4                    | CLKP      |

| 46         | 523.11                     | -1144.4                    | DGND      |

| 47         | 419.54                     | -1144.4                    | DATA1N    |

| 48         | 315.97                     | -1144.4                    | DATA1P    |

| 49         | 144.73                     | -1144.4                    | DGND      |

| 50         | 41.16                      | -1144.4                    | RCALIB    |

| 51         | -62.41                     | -1144.4                    | AGND      |

| 52         | -165.98                    | -1144.4                    | AGND      |

| 53         | -269.55                    | -1144.4                    | VANA      |

| 54         | -398.07                    | -1144.4                    | VANA      |

| 55         | -501.64                    | -1144.4                    | NC        |

| 56         | -605.22                    | -1144.4                    | VCORE     |

| 57         | -708.78                    | -1144.4                    | NC        |

| 58         | -812.36                    | -1144.4                    | NC        |

| 59         | -915.93                    | -1144.4                    | NC        |

| 60         | -1076.96                   | -1144.4                    | AGND      |

| 61         | -1184.9                    | -1045.38                   | AGND      |

| 62         | -1184.9                    | -152.41                    | VCPNEGIN  |

| 63         | -1184.9                    | -48.84                     | VCPNEGOUT |

| 64         | -1184.9                    | 54.73                      | DGND      |

| 65         | -1184.9                    | 158.3                      | AGND      |

| 66         | -1184.9                    | 261.87                     | VANA      |

| 67         | -1184.9                    | 365.44                     | VCORE     |

| 68         | -1184.9                    | 469                        | VCPPOSIN  |

| 69         | -1184.9                    | 572.58                     | VCPPOSOUT |

DS13170 - Rev 10 page 12/30

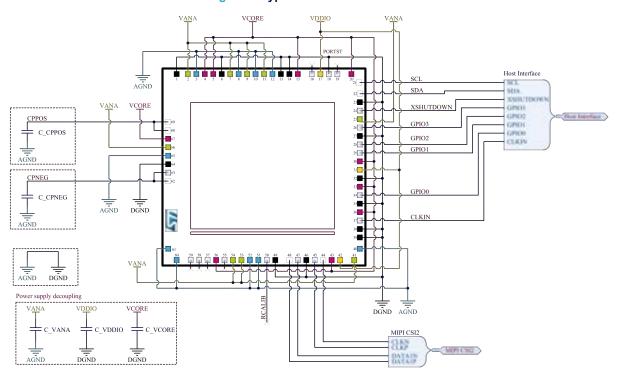

## Application schematic

Capacitor values should be based on capacitor positions (embedded in the camera module or external to the camera module).

Table 6. Capacitor needs

| Capacitor name | Associated pin name    | Capacitor position | Typical voltage | Minimum capacitor | Typical capacitor | Maximum capacitor  | Operating frequencies | Capacitor<br>GND | Purpose           |

|----------------|------------------------|--------------------|-----------------|-------------------|-------------------|--------------------|-----------------------|------------------|-------------------|

| C_CPPOS        | CPPOS_IN,<br>CPPOS_OUT | Embedded           | 3.55 V          | 330 nF            | 470 nF            | 550 nF             | 160 MHz               | AGND             | CP tank capacitor |

| C_CPNEG        | CPNEG_IN,<br>CPNEG_OUT | Embedded           | -2.0 V          | 1 µF              | 1.25 µF           | 1.5 µF             | 160 MHz               | AGND             | CP tank capacitor |

| C VDDIO        | VDDIO                  | Embedded           | 1.8 V           |                   |                   |                    | 1 MHZ                 | DGND             | Supply            |

| C_VDDIO        | VDDIO                  | External           | 1.0 V           |                   | 1 μF              |                    |                       |                  | decoupling        |

|                |                        | Embedded           |                 |                   | 470 nF            |                    | 800 MHz               |                  |                   |

| C VCORE        | C_VCORE VCORE External | 1.                 | 1.15 V          |                   |                   | 1 GHz - 1.2<br>GHz | 1 GHz - 1.2<br>GHz    | DGND             | Supply            |

| 0              |                        |                    |                 |                   | 1 µF              |                    | 160 MHz -<br>200 MHz  | 20.12            | decoupling        |

| C MANA         | 0.1/414                | Embedded           | 2.8 V           |                   | 100 nF            |                    | 160 MHz               | AGND             | Supply            |

| C_VANA         | VANA                   | External           | 2.0 V           |                   | 1 μF              |                    | TOU MINZ              | AGND             | decoupling        |

Figure 5. Typical electric schematic

DS13170 - Rev 10 page 13/30

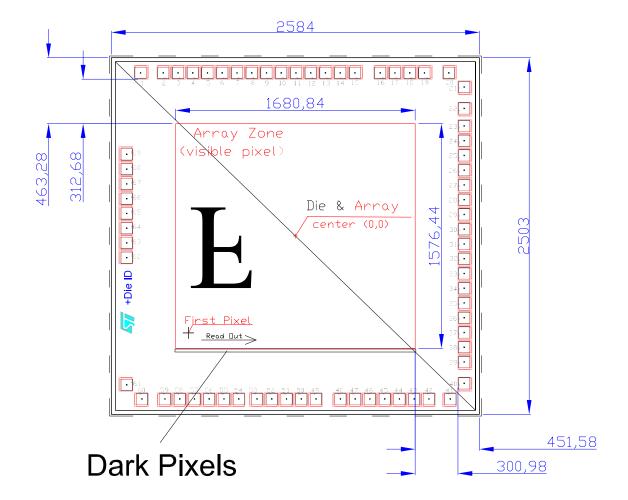

## 6 Die specification

In the table below, the die dimensions are after sawing. The optical center is with the die center as reference.

Table 7. Die size after sawing

| Description          | Min. | Typical | Max. | Unit |

|----------------------|------|---------|------|------|

| X die (after sawing) | 2574 | 2584    | 2594 | μm   |

| Y die (after sawing) | 2493 | 2503    | 2513 | μm   |

| Die thickness        | 143  | 150     | 157  | μm   |

Table 8. Optical center

| Description    | x   | Y   |

|----------------|-----|-----|

| Optical center | 0.0 | 0.0 |

DS13170 - Rev 10 page 14/30

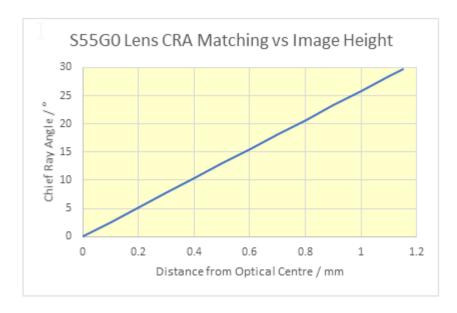

## Chief ray angle (CRA)

Figure 6. Chief ray angle

DS13170 - Rev 10 page 15/30

### 8 Electrical characteristics

The electrical characteristics have been measured under the following conditions:

- Full resolution (644 x 604 pixels)

- Nominal power supply levels

- External clock at 12 MHz

- 185 fps

- 10 bits/pixel

- 1200 Mbits/s on MIPI interface

- 60°C

### 8.1 Operating conditions

Table 9. Operating conditions

| Symbol | Parameter                                            | Min.  | Тур.    | Max.        | Unit |

|--------|------------------------------------------------------|-------|---------|-------------|------|

| VDDIO  | Digital IO power supply                              | 1.7   | 1.8     | 1.9         | V    |

| VANA   | Analog power supply                                  | 2.7   | 2.8     | 2.9         | V    |

| VCORE  | Digital core power supply                            | 1.1   | 1.15    | 1.26        | V    |

| VIO    | IO referenced to VDDIO                               | -0.3  | VDDIO   | VDDIO + 0.5 | V    |

|        |                                                      | Tempe | erature |             |      |

| T JF   | Junction<br>temperature<br>(functional<br>operation) | -30   |         | 85          | °C   |

### 8.2 Power consumption

Table 10. Power consumption

| State      | VDI     | DDIO VCORE |      | ORE  | VANA  |      | Unit |

|------------|---------|------------|------|------|-------|------|------|

| State      | Тур.    | Max.       | Тур. | Max. | Тур.  | Max. |      |

| Streaming  | 0.25    | 0.5        | 46   | 61   | 17.3  | 21   |      |

| SW_STANDBY | 0.0062  | 0.04       | 1.75 | 8    | 0.092 | 0.3  | mA   |

| HW_STANDBY | 0.00135 | 0.04       | 0.5  | 7    | 0.28  | 0.5  |      |

DS13170 - Rev 10 page 16/30

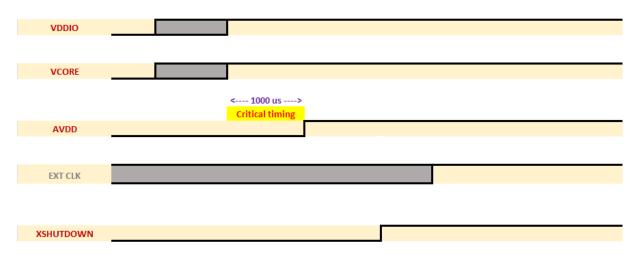

### 8.3 Powerup sequence

- VDDIO and DVDD can be raised in any order but this must be done before AVDD

- Wait at least 1000 μs after VDDIO and VCORE are established before raising the AVDD

- EXT CLOCK can be supplied at any moment

- XSHUTDOWN must be released after AVDD

- Power supplies are considered established when they are above the minimum value required by the datasheet

- AVDD is considered down when it is below 20% of the minimum value targeted by the datasheet

Figure 7. Powerup sequence

DS13170 - Rev 10 page 17/30

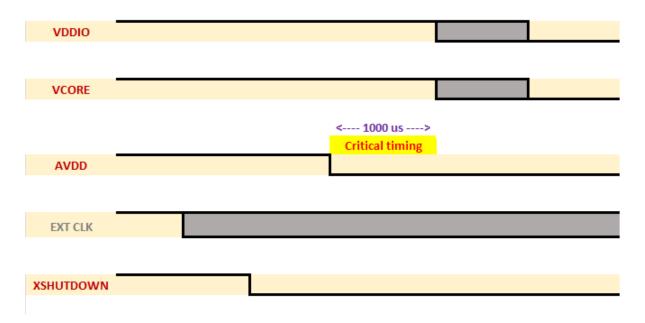

### 8.4 Powerdown sequence

- VDDIO and DVDD can be shut down in any order after AVDD

- AVDD must be shut down at least 1000 μs before VDDIO and DVDD are shut down

- EXT CLOCK can be shut down at any moment

- XSHUTDOWN must be stopped before AVDD

- Power supplies are considered established when they are above the minimum value required by the datasheet

- AVDD is considered down when it is below 20% of the minimum value targeted by the datasheet

Figure 8. Powerdown sequence

DS13170 - Rev 10 page 18/30

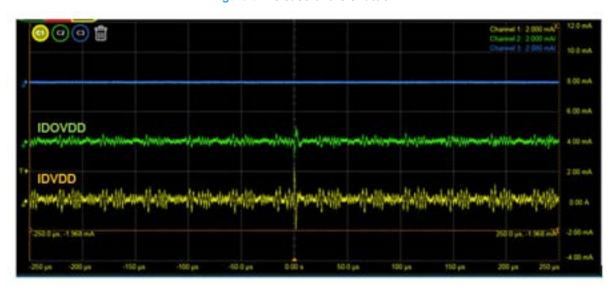

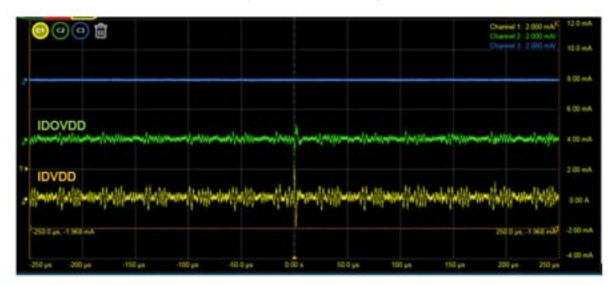

### 8.5 Inrush current

The transient characterization is done at Vnom/Tnom.

Figure 9. Release of the shutdown

Table 11. Overshoot/Undershoot of the DVDD at the release of shutdown

| Supply | Overshoot/Undershoot |

|--------|----------------------|

| DVDD   | 2.29 mA/-1.96 mA     |

Figure 10. Start streaming

Table 12. Overshoot of the VDDIO and DVDD at the start of the stream

| Supply | Overshoot |

|--------|-----------|

| VDDIO  | 6.53 mA   |

| DVDD   | 38 mA     |

DS13170 - Rev 10 page 19/30

## 8.6 AC ripples

Table 13. AC ripples

| Supply | AC ripple (mV) | Frequency range |  |  |

|--------|----------------|-----------------|--|--|

| AVDD   | 10             |                 |  |  |

| DVDD   | 20             | Up to 10 MHz    |  |  |

| VDDIO  | 10             |                 |  |  |

## 8.7 EXTCLK input

**Table 14. EXTCLK input**

| Symbol               | Parameter                                   | Min.                                                         | Max.         | Unit |

|----------------------|---------------------------------------------|--------------------------------------------------------------|--------------|------|

| V <sub>EXTCLKL</sub> | DC-coupled square wave low-level input -0.3 |                                                              | 0.35 x VDDIO | V    |

| V <sub>EXTCLKH</sub> | DC-coupled square wave high-level input     | oupled square wave high-level input 0.65 x VDDIO VDDIO + 0.3 |              | , v  |

| f <sub>EXTCLK</sub>  | Clock input frequency                       | 6                                                            | 27           | MHz  |

| C to Cjitter         | Clock maximum cycle to cycle jitter         | _                                                            | 200          | ps   |

| Duty cycle           | Clock duty cycle                            | 45                                                           | 55           | %    |

| I <sub>EXTCLK</sub>  | I <sub>EXTCLK</sub> Input leakage current   |                                                              | 10           | μA   |

| twl                  | twl Low level width                         |                                                              | 91.67        | ns   |

| twh                  | High level width                            | 16.67                                                        | 91.67        | ns   |

## 8.8 Digital inputs and outputs

Table 15. Digital inputs

| Symbol            | Parameter                 | Min.        | Max.        | Unit |

|-------------------|---------------------------|-------------|-------------|------|

| V <sub>IL</sub>   | Low-level input voltage   | -0.5        | 0.3 x VDDIO | V    |

| V <sub>IH</sub>   | High-level input voltage  | 0.7 x VDDIO | VDDIO + 0.5 | V    |

| I <sub>Leak</sub> | Input leakage current (1) | _           | 10          | μA   |

### 1. For $0 \le VI \le VDDIO$

**Table 16. Digital outputs**

| Symbol           | Parameter                 | Conditions  | Min         | Max  | Unit |

|------------------|---------------------------|-------------|-------------|------|------|

| V <sub>OL</sub>  | Low-level output voltage  | IOL = -4 mA |             | 0.15 | V    |

| V <sub>OH</sub>  | High-level output voltage | IOH = 4 mA  | VDDIO - 0.4 | _    | V    |

| I <sub>max</sub> | Maximum current           | _           |             | 4    | mA   |

DS13170 - Rev 10 page 20/30

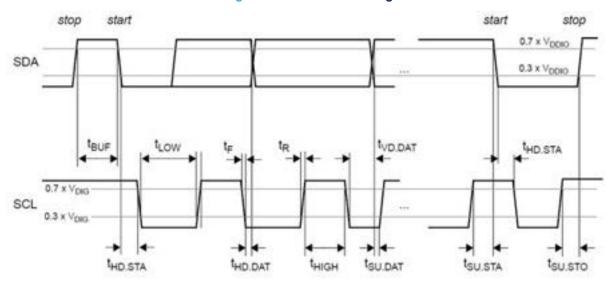

## 8.9 I<sup>2</sup>C interface - SDA, SCL

Table 17. I<sup>2</sup>C interface - SDA, SCL

| Burnetter                                                                                   | Q h l               | Fast mode        |      | Fast mode pl     | us   | 1114 |

|---------------------------------------------------------------------------------------------|---------------------|------------------|------|------------------|------|------|

| Parameter                                                                                   | Symbol              | Min.             | Max. | Min.             | Max. | Unit |

| SCL clock frequency                                                                         | t <sub>SCL</sub>    | 0                | 400  | 0                | 1000 | kHz  |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated |                     | 0.6              | _    | 0.26             | _    |      |

| LOW period of the SCL clock                                                                 | t <sub>LOW</sub>    | 1.3              | _    | 0.5              | _    |      |

| HIGH period of the SCL clock                                                                | t <sub>HIGH</sub>   | 0.6              | _    | 0.26             | _    | μs   |

| Setup time for a repeated START condition                                                   | t <sub>SU.STA</sub> | 0.6              | _    | 0.26             | _    |      |

| Data hold time                                                                              | t <sub>HD.DAT</sub> | 0                | _    | 0                | _    |      |

| Data setup time                                                                             | t <sub>SU.DAT</sub> | 100              | _    | 50               | _    |      |

| Rise time of both SDA and SCL                                                               |                     | 20               | 300  | _                | 120  | ns   |

| Fall time of both SDA and SCL                                                               | t <sub>F</sub>      | 20 x (VDD/5.5 V) | 300  | 15 x (VDD/5.5 V) | 120  |      |

| Setup time for STOP condition                                                               | t <sub>SU.STO</sub> | 0.6              | _    | 0.26             | _    |      |

| Bus free time between a STOP and START condition                                            | t <sub>BUF</sub>    | 1.3              | _    | 0.5              | _    | μs   |

| Capacity load for each bus line                                                             | CO                  | _                | 400  | _                | 550  | pF   |

| Data valid time                                                                             | t <sub>VD.DAT</sub> | _                | 0.9  | _                | 0.45 |      |

| Data valid acknowledge time                                                                 |                     | _                | 0.9  | _                | 0.45 | μs   |

| Noise margin at LOW level for each connected device (including hysteresis)                  |                     | 0.054 x VDD      | _    | 0.054 x VDD      | _    | V    |

| Noise margin at HIGH level for each connected device (including hysteresis)                 | V <sub>nH</sub>     | 0.054 x VDD      | _    | 0.054 x VDD      | _    | V    |

Figure 11. I<sup>2</sup>C interface timing

DS13170 - Rev 10 page 21/30

### 8.10 CSI-2 interface

### 8.10.1 DC specifications

The DC specifications are characterized, not tested.

Table 18. CSI-2 interface, High-speed mode, DC specifications

| Symbol            | Parameter                               | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------|------|------|------|------|

| V <sub>CMTX</sub> | HS transmits static common-mode voltage |      | 200  | 250  |      |

| V <sub>OD</sub>   | HS transmits differential voltage (1)   | 140  | 200  | 270  | mV   |

| V <sub>OHHS</sub> | HS outputs high voltage (1)             |      | _    | 360  |      |

| Z <sub>OS</sub>   | Single-ended output impedance           | 40   | 50   | 62.5 | Ω    |

<sup>1.</sup> Value when driving into load impedance anywhere in the ZID range (80-125  $\Omega$ )

Table 19. CSI-2 interface, Low-power mode, DC specifications

| Symbol           | Parameter                          |     | Тур. | Max. | Unit |

|------------------|------------------------------------|-----|------|------|------|

| V <sub>OH</sub>  | Output high-level                  |     | 1.2  | 1.3  | V    |

| V <sub>OL</sub>  | Output low-level                   |     | _    | 50   | mV   |

| Z <sub>OLP</sub> | Output impedance of LP transmitter | 110 | _    | _    | Ω    |

### 8.10.2 AC specifications

Table 20. CSI-2 interface, High-speed mode, AC specifications

| Symbol                            | Parameter                                        | Min.    | Тур. | Max.   | Unit   |

|-----------------------------------|--------------------------------------------------|---------|------|--------|--------|

| _                                 | Data rate                                        | _       | 804  | _      | Mbit/s |

| t <sub>clkp</sub>                 | Average data period                              | _       | 1.25 | _      | ns     |

| t <sub>r</sub> and t <sub>f</sub> | $t_{\rm f}20\%$ - $80\%$ rise time and fall time | 100     | _    | 0.3UI  | ps     |

| t <sub>skew</sub>                 | Data-to-clock skew                               | -0.15UI | _    | 0.15UI | _      |

DS13170 - Rev 10 page 22/30

### 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

#### 9.1 Sawn die information

The tested die is delivered as a sawn die reconstructed into a 100% yield wafer format on blue or UV-tape, and delivered on a metallic ring.

The frames are packed in plastic containers, each including a maximum of 13 double-spaced reconstructed wafer rings.

ST uses various package labels with its reconstructed wafer shipments:

- Labels on RW frames

- Labels on carrier boxes

Figure 12. Sawn die information

Note: Sawn die size = -10  $\mu$ m

DS13170 - Rev 10 page 23/30

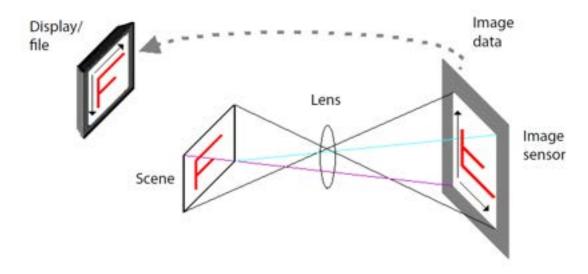

Figure 13. Image orientation

This document is related to the die so the image orientation (depicted in this document with an "F" symbol) shows the image as it is captured by the sensor.

The pixel readout is fully programmable (x and y flip) but the default read fashion is from right to left and top to bottom as shown in Figure 13. Image orientation. This is illustrated by the "F" symbol orientation.

DS13170 - Rev 10 page 24/30

### 10 PNPID

STMicroelectronics is registered as SMO in the PNPID registry since 14th June 2007. The PNPID for the VD55G0 sensor is SMO55F0.

DS13170 - Rev 10 page 25/30

## 11 Ordering information

### Table 21. Order codes

| Order code    | Description |

|---------------|-------------|

| VD55G0CCA1/RW | Bare die    |

DS13170 - Rev 10 page 26/30

## **Revision history**

Table 22. Document revision history

| Date        | Version | Changes               |

|-------------|---------|-----------------------|

| 16-Apr-2024 | 10      | First public release. |

DS13170 - Rev 10 page 27/30

## **Contents**

| Acronyms and abbreviations2 |            |                                             |    |  |

|-----------------------------|------------|---------------------------------------------|----|--|

| Ove                         | rview      |                                             | 3  |  |

| Fun                         | ctional c  | description                                 | 4  |  |

| 3.1                         | Interfac   | ces                                         | 4  |  |

|                             | 3.1.1      | Inter-integrated circuit (I <sup>2</sup> C) | 4  |  |

|                             | 3.1.2      | Camera serial interface (CSI)               | 4  |  |

| 3.2                         | Power      | supplies                                    | 4  |  |

| 3.3                         | Clock.     |                                             | 4  |  |

| 3.4                         | Video pipe |                                             |    |  |

|                             | 3.4.1      | Pattern generation                          | 6  |  |

|                             | 3.4.2      | Defective pixel correction                  | 6  |  |

|                             | 3.4.3      | Dark calibration                            | 6  |  |

|                             | 3.4.4      | Auto exposure                               | 6  |  |

|                             | 3.4.5      | Digital binning                             | 6  |  |

|                             | 3.4.6      | Embedded status lines                       | 7  |  |

|                             | 3.4.7      | Output interface (OIF)                      | 7  |  |

|                             | 3.4.8      | Context                                     |    |  |

|                             | 3.4.9      | Subsampling                                 |    |  |

|                             | 3.4.10     | Crop                                        |    |  |

| 3.5                         | •          | ronization modes                            |    |  |

| 3.6                         | Genera     | al purpose input/outputs (GPIOs)            | 8  |  |

| 3.7                         |            | ises                                        |    |  |

| Pin                         | descript   | tion and assignment                         | 10 |  |

| App                         | lication   | schematic                                   | 13 |  |

| Die                         | specifica  | ation                                       |    |  |

|                             |            | ngle (CRA)                                  |    |  |

|                             | •          | naracteristics                              |    |  |

| 8.1                         |            | ting conditions                             |    |  |

| 8.2                         |            | consumption                                 |    |  |

| 8.3                         |            | up sequence                                 |    |  |

| 8.4                         |            | down sequence                               |    |  |

| 8.5                         |            | current                                     |    |  |

| 8.6                         |            | oles                                        |    |  |

| 8.7                         |            |                                             |    |  |

| 0.7                         | LAIUL      | _K input                                    | 20 |  |

|   | 9.1  | Sawn die information                  | 23 |  |  |

|---|------|---------------------------------------|----|--|--|

| 9 |      | kage information                      |    |  |  |

|   |      | 8.10.2 AC specifications              |    |  |  |

|   |      | 8.10.1 DC specifications              |    |  |  |

|   | 8.10 | CSI-2 interface                       |    |  |  |

|   | 8.9  | I <sup>2</sup> C interface - SDA, SCL |    |  |  |

|   | 8.8  | Digital inputs and outputs            |    |  |  |

|   |      |                                       |    |  |  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

DS13170 - Rev 10 page 30/30