## **Complete Connected LED Driver Power Solution**

# NCL31000, NCL31001

#### Description

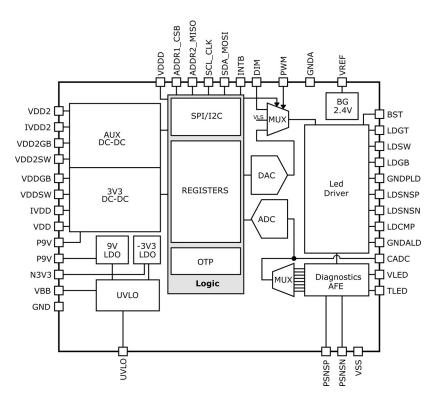

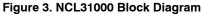

The NCL31000 is a new member of the ON Semiconductor LED driver family specifically targeting luminaire applications. NCL31000 incorporates a high efficient buck LED driver. The LED driver supports both high-bandwidth analog dimming and PWM dimming down to zero current. NCL31000 includes an integrated fixed 3V3 DC-DC and one adjustable DC-DC. A diagnostics block incorporates an ADC, which measures input and LED output currents, voltages, LED temperature, DC/DC voltages and currents. Fast safety mechanisms protect the critical blocks of the chip. The diagnostic measurements are available together with a flexible status reporting and interrupt mechanism. NCL31001 is the same as NCL31000 except that it does not include both DC-DC converters. The combination of NCL31000 and NCL31001 is ideal for dual channel solutions.

#### **Features**

- Wide Input Voltage Range: 21.5 V to 57 V

- Proprietary 100 W+ Applications

- Integrated 3.3 V Buck Convertor (Only for NCL31000)

- Integrated Adjustable Buck Convertor 2.5 24 V (Only for NCL31000)

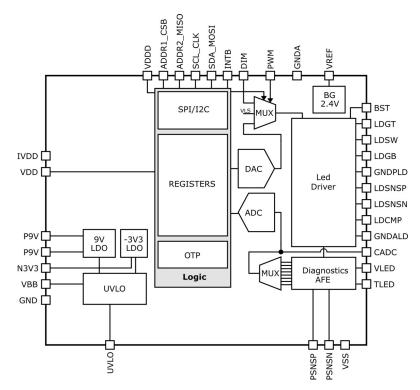

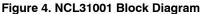

- Integrated High Efficiency Buck LED Driver

- Adjustable Switching Frequency 44.4 kHz to 1 MHz

- Deep Dimming to Zero with Accuracy of 0.1% Using Internal Precision 2.4 V Reference

- Best in Class Linearity

- High Modulation Bandwidth (~50 kHz)

- Visual Light Communication Capable

- ◆ Yellow–Dot<sup>™</sup> Compliant

- Internal DIM DAC for Independent LED Control During Micro-controller Re-flashing (Warm Boot)

- Low EMI Reference Design

- I<sup>2</sup>C/SPI Interface (I/S Suffix)

- High Accuracy Diagnostic Functions to Measure Voltages/Currents

- Protection against LED Shorts & Opens

- LED Over/Under Voltage & Over Current Protection

- Chip Over Current Protection

- Chip & LED Over Temperature Protection

- Junction Temperature Range of -40°C to +125°C

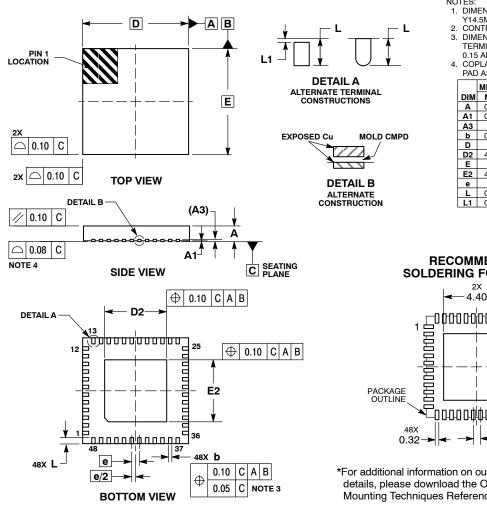

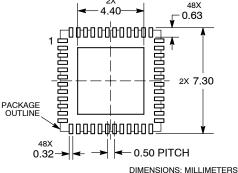

- Available in 48-pin QFN 7x7

- These Devices are Pb-Free and are RoHS Compliant

### **ON Semiconductor®**

www.onsemi.com

QFN48 7x7. 0.5P CASE 485EP

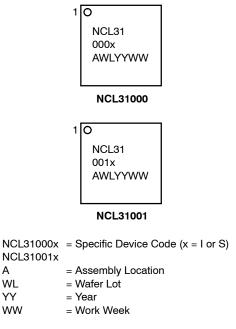

#### MARKING DIAGRAM

#### **ORDERING INFORMATION**

А

YY

See detailed ordering and shipping information on page 2 of this data sheet.

#### **DEVICE ORDERING INFORMATION**

| Device         | DC-DC Converters | Serial Bus       | Shipping <sup>†</sup> |

|----------------|------------------|------------------|-----------------------|

| NCL31000MNITWG | Yes              | l <sup>2</sup> C | 2500 / Tape & Reel    |

| NCL31000MNSTWG | Yes              | SPI              | 2500 / Tape & Reel    |

| NCL31001MNITWG | No               | l <sup>2</sup> C | 2500 / Tape & Reel    |

| NCL31001MNSTWG | No               | SPI              | 2500 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

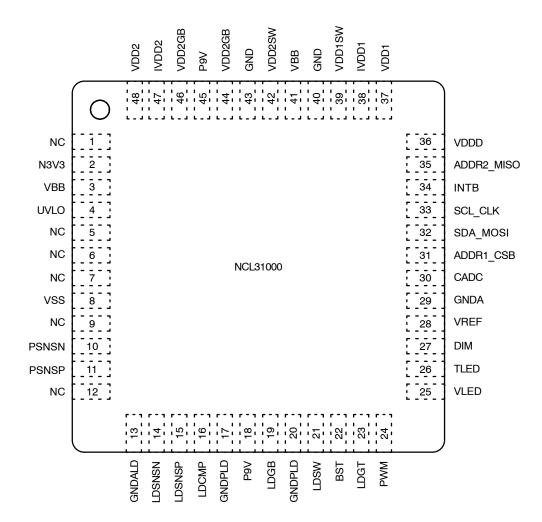

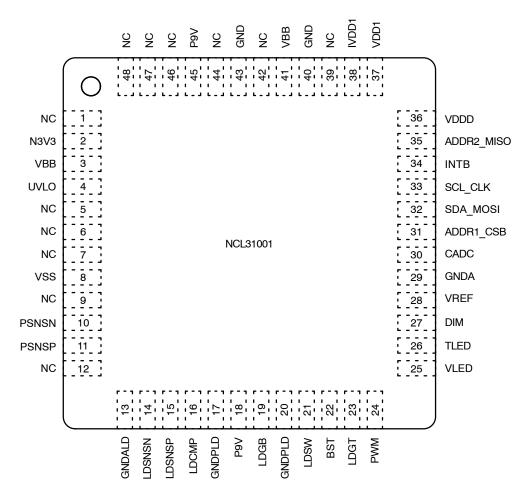

Figure 1. Pin-out NCL31000 in 48-pin QFN (Top View)

#### PIN DESCRIPTION

| Pin No. | Signal Name | Туре   | Description                                                                                                          |

|---------|-------------|--------|----------------------------------------------------------------------------------------------------------------------|

| 1       | NC          |        |                                                                                                                      |

| 2       | N3V3        | Power  | –3V3 LDO output. Decouple to VBB (pin 3) with a 1 $\mu\text{F}$ capacitor.                                           |

| 3       | VBB         | Power  | Positive input power. Connect to the positive terminal of the DC power supply.                                       |

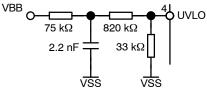

| 4       | UVLO        | Analog | Under-voltage lockout pin. Keep capacitance on this pin versus VSS below 100 pF                                      |

| 5       | NC          |        |                                                                                                                      |

| 6       | NC          |        |                                                                                                                      |

| 7       | NC          |        |                                                                                                                      |

| 8       | VSS         | Power  | Negative input power. Connect to the negative terminal of the DC power supply.                                       |

| 9       | NC          |        |                                                                                                                      |

| 10      | PSNSN       | Input  | Negative input current sense line. Connect to VSS at the negative side of the external input current sense resistor. |

| 11      | PSNSP       | Input  | Positive input current sense line. Connect to the positive side of the external input current sense resistor.        |

| 12      | NC          |        |                                                                                                                      |

| 13      | GNDALD      | Power  | Application ground. Return for the LED Buck compensation network.                                                    |

| 14      | LDSNSN      | Input  | Negative LED current sense line. Connect to the GND side of LDSNS.                                                   |

| 15      | LDSNSP      | Input  | Positive LED current sense line. Connect to the positive side of LDSNS.                                              |

#### PIN DESCRIPTION (continued)

| Pin No. | Signal Name | Туре         | Description                                                                                                                                       |

|---------|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      | LDCOMP      | Analog       | Compensation pin for the LED driver.                                                                                                              |

| 17      | RTNPLD      | Power        | Application ground. LED Buck power return.                                                                                                        |

| 18      | P9V         | Power        | 9 V gate drive voltage regulator output. Decouple to GNDPLD with a 1 $\mu F$ capacitor. Connect to P9V (pin 45) with a trace on the PCB.          |

| 19      | LDGB        | Output       | LED buck convertor bottom switch gate driver.                                                                                                     |

| 20      | GNDPLD      | Power        | Application ground. LED Buck power return.                                                                                                        |

| 21      | LDSW        | Power        | LED buck convertor switching node.                                                                                                                |

| 22      | BST         | Power        | Boost voltage for top switch gate drive. Decouple to LDSW with a 100 nF capacitor.                                                                |

| 23      | LDGT        | Output       | LED buck convertor bottom switch gate driver.                                                                                                     |

| 24      | PWM         | Input        | PWM Dimming input.                                                                                                                                |

| 25      | VLED        | Input        | LED string voltage measurement. Connect to GND when not used.                                                                                     |

| 26      | TLED        | Input        | LED string NTC resistor divider measurement point. Connect to GND when not used.                                                                  |

| 27      | DIM         | Analog       | Analog Dimming input.                                                                                                                             |

| 28      | VREF        | Analog       | Reference precision voltage output. Decouple with a 2.2 $\mu$ F capacitor.                                                                        |

| 29      | RTNA        | Power        | Application ground. Analog return.                                                                                                                |

| 30      | CADC        | Analog       | ADC filter capacitor connection. Decouple to GNDA with a 10 nF capacitor.                                                                         |

| 31      | ADDR1_CSB   | Input        | I <sup>2</sup> C Address for I <sup>2</sup> C mode. Tie to GND, VDDD or leave floating for alternative I <sup>2</sup> C address. CSB in SPI mode. |

| 32      | SDA_MOSI    | Input/Output | I <sup>2</sup> C Data line. External pull-up resistor required. MOSI in SPI mode.                                                                 |

| 33      | SCL_CLK     | Input        | I <sup>2</sup> C Clock line. External pull-up resistor required. CLK in SPI mode.                                                                 |

| 34      | INTB        | Open Drain   | I <sup>2</sup> C Interrupt pin. External pull-up resistor required.                                                                               |

| 35      | ADDR2_MISO  | Input        | I <sup>2</sup> C Address. Tie to GND or leave floating for alternative I <sup>2</sup> C address. MISO in SPI mode.                                |

| 36      | VDDD        | Power        | 3V3 power input for the NCL31000 digital circuitry.                                                                                               |

| 37      | VDD1        | Power        | 3V3 power output for the chip and external circuitry.                                                                                             |

| 38      | IVDD1       | Input        | Current measurement for VDD1 regulator. Connect to the positive terminal of the VDD1 sense resistor.                                              |

| 39      | VDD1SW      | Power        | VDD1 buck convertor switching node.                                                                                                               |

| 40      | GND         | Power        | Application ground. Ground connection for the VDD1 and VDD2 DC/DC convertors.                                                                     |

| 41      | VBB         | Power        | Positive input power. Decouple to the GND with a 1 $\mu\text{F}$ capacitor. Connect to the positive terminal of the DC power supply.              |

| 42      | VDD2SW      | Power        | VDD2 buck convertor switching node.                                                                                                               |

| 43      | GND         | Power        | Application ground. Ground connection for the VDD1 and VDD2 DC/DC convertors                                                                      |

| 44      | VDD2GB      | Output       | VDD2 buck convertor bottom switch gate driver.                                                                                                    |

| 45      | P9V         | Power        | 9 V gate drive voltage input. Decouple to GND with a 100 nF capacitor.<br>Connect to P9V (pin 18) with a trace on the PCB.                        |

| 46      | VDD1GB      | Output       | VDD1 buck convertor bottom switch gate driver.                                                                                                    |

| 47      | IVDD2       | Input        | Current measurement for VDD2 regulator. Connect to the positive terminal of the VDD2 sense resistor.                                              |

| 48      | VDD2        | Power        | VDD2 power output for external circuitry.                                                                                                         |

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                       | Parameter                          | Min     | Max                   | Unit |

|------------------------------|------------------------------------|---------|-----------------------|------|

| VBB                          | Input Power Supply vs. VSS         | -0.3    | 70                    | V    |

| GND, GNDPLD, GNDA,<br>GNDALD | Application Ground vs. VSS         | -0.3    | VBB + 0.3             | V    |

| BST                          | Analog Output vs. LDSW             | -0.3    | 11                    | V    |

| LDGT                         | Analog Output vs. GND              | -0.3    | Min (70, VBB + 11)    | V    |

| LDSW                         | Analog Output vs. GND              | -0.3    | VBB+0.3               | V    |

| PSNSN, PSNSP                 | Analog Input vs. VSS               | -0.3    | 3.6                   | V    |

| LDSNSN, LDSNSP               | Analog Input vs. GND               | -0.3    | 0.3                   |      |

| VDD1                         | 3.3 V Analog Supply vs. GND        | -0.3    | 3.6                   | V    |

| VDDD                         | 3.3 V Digital Supply vs. GND       |         |                       |      |

| ADDR1_CSB                    | Digital Input/Output vs. GND       |         |                       |      |

| ADDR2_MISO                   | Digital Input/Output vs. GND       |         |                       |      |

| VREF                         | Analog Output vs. GND              |         |                       |      |

| DIM                          | Analog Input vs. GND               |         |                       |      |

| CADC                         | Analog Output vs. GND              |         |                       |      |

| LDCOMP                       | Compensation Pin vs. GND           |         |                       |      |

| IVDD1                        | Analog Input vs. GND               | -0.3    | Min (3.6, VDD1 + 0.3) | V    |

| SDA_MOSI                     | Digital Input/Output vs. GND       | -0.3    | 5.5                   | V    |

| SCL_SCK                      | Digital Input vs. GND              |         |                       |      |

| INTB                         | Open Drain Digital Output vs. GND  |         |                       |      |

| P9V                          | Analog Output vs. GND              | -0.3    | 11                    | V    |

| VDD1GB, VDD2GB               | Analog Output vs. GND              |         |                       |      |

| LDGB                         | Analog Output vs. GND              |         |                       |      |

| N3V3                         | Analog Output vs. GND              | VBB-3.6 | VBB + 0.3             | V    |

| VDD2                         | Analog Input vs. GND               | -0.3    | VBB + 0.3             | V    |

| VLED                         | HV tolerant Input vs. GND          |         |                       |      |

| PWM                          | HV tolerant Input vs. GND          |         |                       |      |

| TLED                         | HV tolerant Input vs. GND          |         |                       |      |

| IVDD2                        | Analog Input vs. GND               |         |                       |      |

| VDD1SW                       | Analog Output vs. GND              | -0.6    | VBB + 11              | V    |

| VDD2SW                       | Analog Output vs. GND              |         |                       |      |

| T <sub>STRG</sub>            | Storage Temperature                | -55     | +150                  | °C   |

| TJ                           | Junction Temperature               | -40     | +125                  | °C   |

| ESD-HBM                      | Human Body Model; EIA-JESD-A114    | 2       | -                     | kV   |

| ESD-CDM                      | Charged Device Model; ESD-STM5.3.1 | 500     | -                     | V    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol           | Parameter                                  |     | Мах  | Unit |

|------------------|--------------------------------------------|-----|------|------|

| VBB              | Input Power Supply (VBB vs. VSS)           |     | 57   | V    |

| V <sub>I_D</sub> | Digital Inputs SCL, SDA, INTB, PWM vs. GND | 0   | 5    | V    |

| VTLED            | Temperature Sense Analog Input vs. GND     | 0   | VDD1 | V    |

| T <sub>A</sub>   | Ambient Temperature                        | -40 | +85  | °C   |

| Т <sub>Ј</sub>   | Junction Temperature                       | -40 | +125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### THERMAL CHARACTERISTICS

| Symbol | Characteristic                       | Value | Unit |

|--------|--------------------------------------|-------|------|

| θJC    | Thermal Resistance, Junction-to-Case | 38    | °C/W |

| θJA    | Thermal Resistance, Junction-to-Air  | 128   | °C/W |

1. 0JA is obtained with 1S1P test board (1 signal - 1 plane) and natural convection. Refer to JEDEC JESD51 for details

#### **ELECTRICAL CHARACTERISTICS**

| Symbol         | Parameter                                        | Condition                             | Min   | Тур   | Max   | Unit |  |  |

|----------------|--------------------------------------------------|---------------------------------------|-------|-------|-------|------|--|--|

| OSCILLATOR     | OSCILLATOR                                       |                                       |       |       |       |      |  |  |

| OSC_FREQ       | Oscillation Frequency                            |                                       | 7.6   | 8     | 8.4   | MHz  |  |  |

| UNDER VOLTAG   | JNDER VOLTAGE LOCK-OUT CHARACTERISTICS           |                                       |       |       |       |      |  |  |

| UVLO_H         | VBB UVLO Threshold Voltage (Note 2)              | VBB rising                            | 1.15  | 1.23  | 1.3   | V    |  |  |

| UVLO_L         | VBB UVLO Threshold Voltage (Note 2)              | VBB falling                           | 1.09  | 1.17  | 1.26  | V    |  |  |

| UVLO_hyst      | UVLO Threshold Hysteresis                        |                                       | 30    | 53    | 75    | mV   |  |  |

| CONSUMPTIONS   | 6 (VBB = 53 V)                                   |                                       |       |       |       |      |  |  |

| ldd_on,0       | Operating Current                                | CTRL = 0; VDD1 Non-switching          | -     | 2.03  | -     | mA   |  |  |

| ldd_on,1       | Operating Current w. VDD2                        | CTRL = 1; VDD1, VDD2<br>Non-switching | -     | 2.12  | -     | mA   |  |  |

| ldd_on,2       | Operating Current w. Metrology                   | CTRL = 4; VDD1 Non-switching          | -     | 2.06  | -     | mA   |  |  |

| ldd_on,3       | Operating Current w. VDD2 & Metrology            | CTRL = 5; VDD1, VDD2<br>Non-switching | -     | 2.15  | _     | mA   |  |  |

| VDD1 & VDD2 DO | CDC ELECTRICAL SPECIFICATIONS                    |                                       |       |       |       |      |  |  |

| VDD1x_Freq     | Switching Frequency                              | JIT_EN = 0                            | 126.6 | 133.3 | 140   | kHz  |  |  |

| N3V3           | Internal VBB-N3V3 Voltage                        | $0 \le I \le 5 \text{ mA}$            | 3.13  | 3.3   | 3.47  | V    |  |  |

| P9V            | Internal P9V Voltage<br>(Generated in LED Block) | $0 \le I \le 20 \text{ mA}$           | 8.55  | 9     | 9.45  | V    |  |  |

| VDD1xGB_Rpu    | LS Gate Driver Pull-up Resistance                |                                       | 15    | 28    | 65    | Ω    |  |  |

| VDD1xGB_Rpd    | LS Gate Driver Pull-down Resistance              |                                       | 2     | 3.25  | 6.5   | Ω    |  |  |

| VDD1xGB_Tr     | LS Gate Driver Rise Time                         |                                       | 10    | 20    | 52    | ns   |  |  |

| VDD1xGB_Tf     | LS Gate Drive Fall Time                          |                                       | 3     | 6     | 16    | ns   |  |  |

| VDD1 MAIN DCD  | C ELECTRICAL SPECIFICATIONS                      |                                       |       |       |       |      |  |  |

| DC3V3_VDD1     | Main Supply Output Voltage                       |                                       | 3.234 | 3.3   | 3.366 | V    |  |  |

| DC3V3_ILMT     | Peak Inductor Current Limit                      | R <sub>sns</sub> = 0.75 Ω             | 230   | 300   | 370   | mA   |  |  |

| VDD1_Ton,min   | Minimum ON Time                                  |                                       | 50    | 110   | 200   | ns   |  |  |

| VDD1_Ton,min   | Minimum OFF Time                                 |                                       | 50    | 88    | 200   | ns   |  |  |

| VDD1_HS_Ron    | Top Switch on Resistance                         |                                       | 1.5   | 3.3   | 7.5   | Ω    |  |  |

| I_VDDD         | Operating Current on VDDD                        | CTRL = 0                              | -     | 3.15  | -     | mA   |  |  |

### ELECTRICAL CHARACTERISTICS (continued)

| Symbol        | Parameter                         | Condition                           | Min   | Тур   | Max   | Unit |

|---------------|-----------------------------------|-------------------------------------|-------|-------|-------|------|

| VDD1 MAIN DCD | C ELECTRICAL SPECIFICATIONS       |                                     |       | •     |       |      |

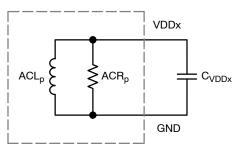

| VDD1_ACRp     | Equivalent AC Parallel Resistance | R <sub>sns</sub> = 0.75 Ω; CCM      | -     | 0.6   | -     | Ω    |

| VDD1_ACLp     | Equivalent AC Parallel Inductance | R <sub>sns</sub> = 0.75 Ω; CCM      | -     | 149   | -     | μΗ   |

| VDDD RESET EL | ECTRICAL SPECIFICATIONS           |                                     |       |       |       |      |

| VDD1_POR_LH   | VDD1(D) Reset Threshold H         | VDD1(D) Rising                      | 2.8   | 2.9   | 3.05  | V    |

| VDD1_POR_HL   | VDD1(D) Reset Threshold L         | VDD1(D) Falling                     | 2.5   | 2.7   | 2.8   | V    |

| VDD1_POR_HY   | VDD1(D) Reset Hysteresis          |                                     | 0.2   | 0.3   | 0.4   | V    |

| VDD2 AUXILIAR | / DCDC ELECTRICAL SPECIFICATIONS  | 5                                   |       |       |       |      |

| DCAUX_VDD2    | Aux Supply Output Voltage         | 5V0 (VDD2_SEL = 2)                  | 4.9   | 5     | 5.1   | V    |

|               |                                   | 7V2 (VDD2_SEL = 6)                  | 7.056 | 7.2   | 7.344 | V    |

|               |                                   | 2V5 (VDD2_SEL = 0)                  | 2.45  | 2.5   | 2.55  | V    |

|               |                                   | 3V3 (VDD2_SEL = 4)                  | 3.234 | 3.3   | 3.366 | V    |

|               |                                   | 10V (VDD2_SEL = 1)                  | 9.8   | 10    | 10.2  | V    |

|               |                                   | 12V (VDD2_SEL = 5)                  | 11.76 | 12    | 12.24 | V    |

|               |                                   | 15V (VDD2_SEL = 3)                  | 14.7  | 15    | 15.3  | V    |

|               |                                   | 24V (VDD2_SEL = 7)                  | 23.52 | 24    | 24.48 | V    |

| DCAUX_ILMT    | Peak Inductor Current Limit       | 5V0; R <sub>sns</sub> = 0.22 Ω      | 882   | 948   | 1014  | mA   |

|               |                                   | 7V2; R <sub>sns</sub> = 0.22 Ω      | 601   | 668   | 750   | mA   |

|               |                                   | 2V5; R <sub>sns</sub> = 0.20 Ω      | 811   | 872   | 933   | mA   |

|               |                                   | 3V3; R <sub>sns</sub> = 0.20 Ω      | 802   | 862   | 922   | mA   |

|               |                                   | 10V; R <sub>sns</sub> = 0.33 Ω      | 544   | 604   | 664   | mA   |

|               |                                   | 12V; R <sub>sns</sub> = 0.33 Ω      | 544   | 604   | 664   | mA   |

|               |                                   | 15V; R <sub>sns</sub> = 0.33 Ω      | 538   | 598   | 678   | mA   |

|               |                                   | 24V; R <sub>sns</sub> = 0.36 Ω      | 450   | 547   | 650   | mA   |

| VDD2_Ton,min  | Minimum ON Time                   |                                     | 50    | 87    | 150   | ns   |

| VDD2_Ton,min  | Minimum OFF Time                  |                                     | 50    | 84    | 150   | ns   |

| VDD2_HS_Ron   | Top Switch on Resistance          |                                     | 0.5   | 1.1   | 2.65  | Ω    |

| VDD2_Sx       | Slope Compensation                | 15V; R <sub>sns</sub> = 0.33 Ω      | -     | 0.073 | -     | A/μs |

|               |                                   | 24V; $R_{sns} = 0.36 \ \Omega$      | 0.028 | 0.067 | -     | A/μs |

| VDD2_ACRp     | Equivalent AC Parallel Resistance | 5V0; R <sub>sns</sub> = 0.22 Ω; CCM | -     | 0.23  | -     | Ω    |

|               |                                   | 7V2; $R_{sns} = 0.22 \Omega$ ; CCM  | -     | 0.53  | -     | Ω    |

|               |                                   | 2V5; R <sub>sns</sub> = 0.20 Ω; CCM | -     | 0.12  | -     | Ω    |

|               |                                   | 3V3; R <sub>sns</sub> = 0.20 Ω; CCM | -     | 0.15  | -     | Ω    |

|               |                                   | 10V; R <sub>sns</sub> = 0.33 Ω; CCM | _     | 1.22  | -     | Ω    |

|               |                                   | 12V; R <sub>sns</sub> = 0.33 Ω; CCM | _     | 1.16  | -     | Ω    |

|               |                                   | 15V; R <sub>sns</sub> = 0.33 Ω; CCM | -     | 0.92  | -     | Ω    |

|               |                                   | 24V; R <sub>sns</sub> = 0.36 Ω; CCM | -     | 2.09  | -     | Ω    |

### ELECTRICAL CHARACTERISTICS (continued)

| Symbol                | Parameter                                            | Condition                           | Min    | Тур   | Max    | Unit |

|-----------------------|------------------------------------------------------|-------------------------------------|--------|-------|--------|------|

| VDD2 AUXILIARY        | DCDC ELECTRICAL SPECIFICATIONS                       |                                     |        |       |        |      |

| VDD2_ACLp             | Equivalent AC Parallel Inductance                    | 5V0; R <sub>sns</sub> = 0.22 Ω; CCM | -      | 60    | -      | μH   |

|                       |                                                      | 7V2; R <sub>sns</sub> = 0.22 Ω; CCM | -      | 120   | -      | μH   |

|                       |                                                      | 2V5; R <sub>sns</sub> = 0.20 Ω; CCM | -      | 29    | -      | μH   |

|                       |                                                      | 3V3; R <sub>sns</sub> = 0.20 Ω; CCM | -      | 38    | -      | μH   |

|                       |                                                      | 10V; R <sub>sns</sub> = 0.33 Ω; CCM | -      | 275   | -      | μH   |

|                       |                                                      | 12V; R <sub>sns</sub> = 0.33 Ω; CCM | -      | 275   | -      | μH   |

|                       |                                                      | 15V; R <sub>sns</sub> = 0.33 Ω; CCM | -      | 229   | -      | μH   |

|                       |                                                      | 24V; R <sub>sns</sub> = 0.36 Ω; CCM | -      | 514   | -      | μH   |

| LED DRIVER ELE        | CTRICAL SPECIFICATIONS                               |                                     |        |       |        | -    |

| VBB                   | Input Voltage Range for Stable Output                |                                     | 21.5   | _     | 57     | V    |

| VLED                  | LED String Voltage vs. GND                           |                                     | 4      | -     | 38     | V    |

| VDIM                  | Analog DIM Input vs. GND                             |                                     | 0      | -     | 2.4    | V    |

| ILED (Note 4)         | LED Current Range                                    |                                     | 0      | -     | 3      | А    |

| VSNS (Note 5)         | Sense Resistor Voltage                               |                                     | -0.24  | _     | 0.3    | V    |

| VCSA_0 (Note 6)       | Sense Amplifier Output Voltage [Inputs Sho           | orted]                              | 197    | 200   | 205    | mV   |

| ILED_OFFS<br>(Note 7) | LED Current Regulation Offset Error Relative to VREF |                                     | -0.125 | _     | 0.2    | %    |

| ILED_GAIN<br>(Note 8) | LED Current Regulation Gain Error                    |                                     | -2     | _     | 2      | %    |

| FAST CURRENT-         | MODE AMPLIFIER                                       |                                     |        |       |        |      |

| LED_CSNSF_<br>GAIN    | Current-mode Loop Amplifier Gain                     |                                     | 2.97   | 3.0   | 3.03   |      |

| LED DRIVER SAV        | VTOOTH SLOPE COMPENSATION ELECT                      | RICAL SPECIFICATIONS                |        |       |        |      |

| SLP1_1                | Slope Compensation 1 with SLP1<1:0> = 0              | 00                                  | 0.07   | 0.1   | 0.13   | V/μs |

| SLP1_2                | Slope Compensation 1 with SLP1<1:0> = 0              | 01                                  | 0.14   | 0.2   | 0.26   | V/μs |

| SLP1_3                | Slope Compensation 1 with SLP1<1:0> = 1              | 10                                  | 0.21   | 0.3   | 0.39   | V/μs |

| SLP1_4                | Slope Compensation 1 with SLP1<1:0> = 1              | 11                                  | 0.28   | 0.4   | 0.52   | V/μs |

| SLP2_1                | Slope Compensation 2 with SLP2<1:0> = 0              | 00                                  | 0.21   | 0.3   | 0.39   | V/μs |

| SLP2_2                | Slope Compensation 2 with SLP2<1:0> = 0              | 01                                  | 0.28   | 0.4   | 0.52   | V/μs |

| SLP2_3                | Slope Compensation 2 with SLP2<1:0> = 1              | 10                                  | 0.42   | 0.6   | 0.78   | V/μs |

| SLP2_4                | Slope Compensation 2 with SLP2<1:0> = 1              | 11                                  | 0.63   | 0.9   | 1.17   | V/μs |

| LED DRIVER INTI       | ERNAL DAC ELECTRICAL SPECIFICATIO                    | INS                                 |        |       |        |      |

| DIM_DNL               | Internal DIM Differential Nonlinearity               |                                     | -0.5   | 0     | 0.5    | LSB  |

| DIM_INL               | Internal DIM Integral Nonlinearity                   |                                     | -0.5   | 0     | 0.5    | LSB  |

| DIM_MAX               | Internal DIM Maximum (Code 0x7F)                     |                                     | 2.376  | 2.4   | 2.424  | V    |

| DIM_MIN               | Internal DIM Minimum (Code 0x09)                     |                                     | 168.75 | 187.5 | 206.75 | mV   |

| DIM_RES               | Internal DIM DAC Resolution                          |                                     | -      | 7     | _      | LSB  |

| LED DRIVER OVE        | R-CURRENT PROTECTION ELECTRICA                       | L SPECIFICATION                     | •      |       | •      |      |

| OCP_VTH_UP            | Comparator Threshold                                 |                                     | 2.95   | 3     | 3.04   | V    |

| LED DRIVER SOF        | T-START /OTA/NON-OVERLAPPING ELI                     | ECTRICAL SPECIFICATION              |        |       |        |      |

| GM                    | Error Amplifier Transconductance gm in Op            | perational Mode                     | 0.5    | 1     | 1.5    | mS   |

| GM_SST                | Error Amplifier Transconductance gm in So            | oft Start Mode                      | 60     | 100   | 180    | μS   |

| Symbol                       | Parameter                                | Condition             | Min   | Тур | Max   | Unit |

|------------------------------|------------------------------------------|-----------------------|-------|-----|-------|------|

| LED DRIVER SO                | FT-START /OTA/NON-OVERLAPPING ELE        | CTRICAL SPECIFICATION |       |     |       |      |

| TON_MIN                      | Minimum ON Time of the HS Driver         |                       | 20    | 63  | 150   | ns   |

| TOFF_MIN                     | Minimum ON Time of the LS Driver         |                       | 20    | 73  | 150   | ns   |

| TNOV                         | Non-overlapping Time                     |                       | 10    | 25  | 50    | ns   |

| REFERENCE VO                 | LTAGE CHARACTERISTICS                    |                       |       |     |       |      |

| VREF                         | Voltage Reference for DIAG/LED/DCDC [IF  | EF < 2 mA]            | 2.394 | 2.4 | 2.406 | V    |

| IREF                         | Voltage Reference Current Consumption    |                       | -     | -   | 3     | mA   |

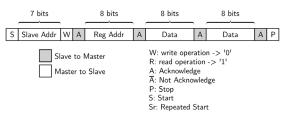

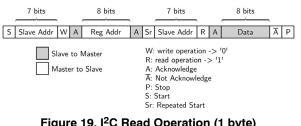

| I <sup>2</sup> C TIMING CHAF | RACTERISTICS (NCL31000I)                 |                       |       |     |       |      |

| f_SCL                        | Interface Clock Frequency                |                       | -     | -   | 400   | kHz  |

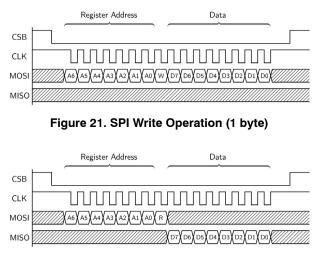

| SPI TIMING CHA               | RACTERISTICS (NCL31000S)                 |                       |       |     |       |      |

| f_SCLK                       | Interface Clock Frequency                |                       | -     | _   | 2     | MHz  |

| DIAGNOSTICS E                | LECTRICAL SPECIFICATION                  |                       |       |     |       |      |

| DIAG_ILED                    | LED Current Measurement Overall Accuracy |                       | -0.6  | _   | 0.6   | %    |

| DIAG_VLED                    | LED Voltage Measurement Overall Accurac  | у                     | -0.8  | _   | 0.8   | %    |

| DIAG_IBB                     | Input Current Measurement Overall Accura | су                    | -1    | -   | 1     | %    |

| DIAG_VBB                     | Input Voltage Measurement Accuracy       |                       | -0.9  | -   | 0.9   | %    |

| DIAG_IVDD1                   | VDD1 Current Measurement Overall Accura  | асу                   | -2    | -   | 2     | %    |

| DIAG_IVDD2                   | VDD2 Current Measurement Overall Accura  | асу                   | -2    | -   | 2     | %    |

| DIAG_VDD1                    | VDD1 Voltage Measurement Overall Accura  | асу                   | -1    | -   | 1     | %    |

| DIAG_VDD2                    | VDD2 Voltage Measurement Overall Accura  | асу                   | -1    | -   | 1     | %    |

| DIAG_TLED                    | TLED Voltage Measurement Overall Accura  | су                    | -1    | -   | 1     | %    |

| DIAG_CONSO                   | DIAG Current Consumption                 |                       | -     | -   | 200   | μA   |

| THERMAL PROT                 | ECTION CHARACTERISTICS                   |                       |       |     |       |      |

| TSD_H                        | Thermal Shutdown, High Threshold         |                       | 141   | 150 | 159   | °C   |

| TSD_L                        | Thermal Shutdown, Low Threshold          |                       | 126   | 135 | 143   | °C   |

| TWRN_H                       | Thermal Warning, High Threshold          |                       | 112   | 120 | 127   | °C   |

| TWRN_L                       | Thermal Warning, Low Threshold           |                       | 101   | 108 | 114   | °C   |

#### ELECTRICAL CHARACTERISTICS (continued)

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

2. Voltage referenced to VSS

3. E.g. after overcurrent timeout

4. This range depends on the sense resistor RSNS.

5. Assume inductor current ripple included. This spec implies that the inductor current ripple size has an upper limit VSNSmin > RSNS x Ippmax / 2.

6. The VCSA voltage is the output of the LED sense amplifier and is the compare voltage for the DIM input. VCSA\_0 is given with the inputs shorted. The VCSA\_0 voltage is the threshold to get exactly zero current.

7. This deviation is the total offset in the loop. It is specified relative to the VREF typical. It is useful for calculating the maximum offset error when using a VREF based solution for accurate dimming to low currents. It is derived from VCSA\_0:

a. ILED\_OFFS<sub>HIGH</sub> = (VCSA\_0<sub>HIGH</sub> – VCSA\_0<sub>TYP</sub>) / VREF

8. This error is a dominant factor in the LED current regulation error at mid and high LED currents. It is specified relative to VREF typical. Assume RSNS = 100 m $\Omega$  and ideal.

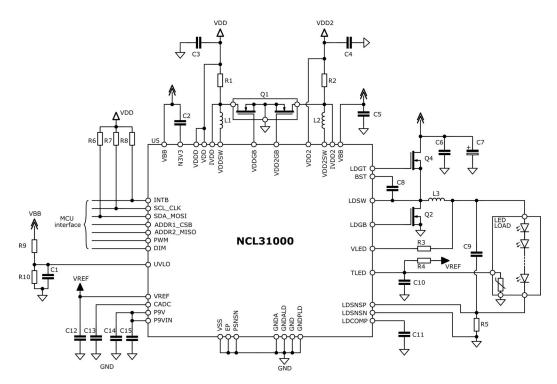

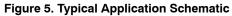

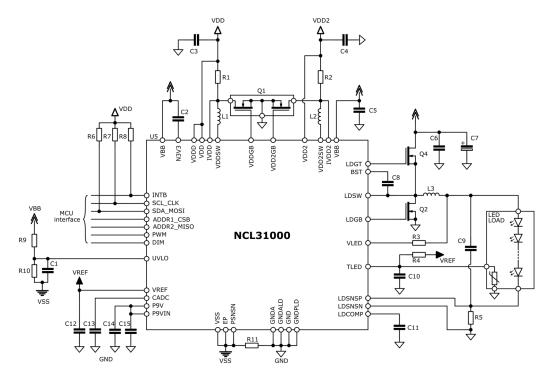

### SIMPLIFIED APPLICATION SCHEMATIC

Figure 6. Typical Application Schematic with Input Current Sense

Figure 7. Typical Application Schematic Dual Channel

| Symbol | Description                                      | Value          | Rating             | Remark    | Reference          |

|--------|--------------------------------------------------|----------------|--------------------|-----------|--------------------|

| C1     | Decoupling                                       | 100 pF         | 10 V               | (Note 9)  |                    |

| C2     | Decoupling, Buffer                               | 1 μF           | 10 V               |           |                    |

| C3     | Output Capacitor for VDD1                        | 22 μF          | 6.3 V              | 1         | C1206C226K9PAC     |

| C4     | Output Capacitor for VDD2                        | 47 μF          | 6.3 V              | (Note 11) | C1210C476M9PAC     |

| C5     | Fast Filter Capacitor for DC-DC's and Chip       | 1 μF           | 100 V              |           | C1210C105K1RAC     |

| C6     | Fast Filter Capacitor for LED Driver             | 2 x 1 μF       | 100 V              |           | C1210C105K1RACTU   |

| C7     | Buffer Capacitor for Application                 | 56 μF          | 80 V               |           | A759MS566M1KAAE045 |

| C8     | LED Bootstrap Capacitor                          | 100 nF         | 25 V               |           |                    |

| C9     | LED Driver Output Capacitors                     | 2 x 470 nF     | 100 V              |           | C0805C471K1RACTU   |

| C13    | Filtering TLED                                   | 100 nF         | 25 V               |           |                    |

| C11    | LED Driver Compensation Capacitor                | 10 nF          | 25 V               |           |                    |

| C12    | Stabilization Capacitor, Buffer VREF             | 2.2 μF         | 10 V               |           |                    |

| C13    | Sample and Hold for ADC                          | 10 nF          | 25 V               |           |                    |

| C14    | Decoupling, Buffer P9V                           | 1 μF           | 25 V               |           |                    |

| C15    | Decoupling P9V                                   | 100 nF         | 25 V               |           |                    |

| R1     | VDD1 Sense Resistor                              | 750 m $\Omega$ |                    |           | RCWE0603R750FKEA   |

| R2     | VDD2 Sense Resistor                              | 200 mΩ         |                    | (Note 11) | RL1220S-R20-F      |

| R3     | Protection Resistor for Overvoltage on VLED Node | 100 Ω          |                    |           | RC0603FR-07100RL   |

| R4     | TLED Resistor                                    | 10 kΩ 1%       |                    |           |                    |

| R5     | LED Driver Current Sense Resistor                | 180 mΩ 1%      | 2 W                | (Note 10) |                    |

| R6     | I <sup>2</sup> C Pull-up                         | 4.7 kΩ         |                    |           |                    |

| R7     | I <sup>2</sup> C Pull-up                         | 4.7 kΩ         |                    |           |                    |

| R8     | Interrupt Pull-up                                | 4.7 kΩ         |                    |           |                    |

| R9     | UVLO (POR @ 35 V)                                | 470 kΩ 1%      |                    |           |                    |

| R10    | UVLO (POR @ 35 V)                                | 16 kΩ 1%       |                    |           |                    |

| R11    | Sense Resistor for Input Current                 | 100 mΩ 1%      | 2 W                |           | CRA2512-FZ-R100ELF |

| L1     | VDD1 Buck Inductor                               | <b>390</b> μΗ  |                    |           | 744777239          |

| L2     | VDD2 Buck Inductor                               | 100 μH         |                    | 1         | 7447714101         |

| L3     | LED Driver Buck Inductor                         | 68 μH          | 2 A <sub>rms</sub> | (Note 10) |                    |

| Q1     | Dual NMOS Bottom Switching Transistor for DC/DCs |                |                    | 1         | FDC8602            |

| Q3     | NMOS Bottom Switching Transistor for LED Driver  |                |                    |           | FDMA037N08L        |

| Q4     | NMOS Top Switching Transistor for LED Driver     |                |                    |           | NVTFS6H880N        |

| U5     |                                                  |                |                    |           | NCL31000           |

#### Table 1. TYPICAL BILL OF MATERIALS - BASED ON SINGLE CHANNEL WITH INPUT CURRENT SENSE

9. Must be smaller than 1 nF.

10. Inductor saturation current and LED current sense resistor depend on the application specifications such as required power, allowed current

ripple. See LED driver section for details. 11. The values for L2, R2 and C4 in the table are specific for the 5 V VDD2 output. Refer to table 6 and 10 for other VDD2 output voltages. General: The schematic does not show EMI filtering required for some applications.

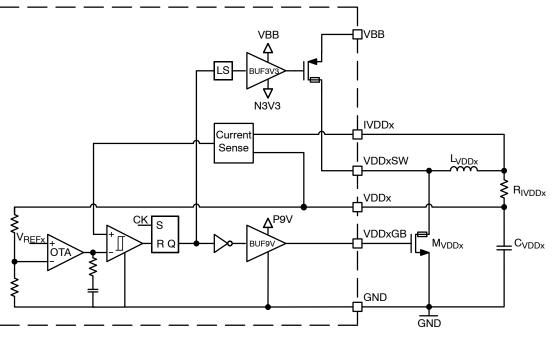

#### **DUAL STEP-DOWN CONVERTER FUNCTIONAL DESCRIPTION**

The NCL31000 incorporates a dual synchronous step-down switching converter for generating two voltage rails. The top mosfets are internal in NCL31000, whereas the bottom mosfets need to be added externally.

The regulators employ a constant-frequency peak current-mode control scheme with internal compensation. The inductor current is sensed trough a resistance in series with the inductor. This also allows the NCL31000 to measure the average output current (see <u>Metrology</u> section). Depending on the load current, the converter operates in Discontinuous Conduction Mode (DCM) or Continuous Conduction Mode (CCM).

The VDD1 regulator, which is automatically enabled when the voltage on the UVLO pin rises above the UVLO\_H treshold, generates a 3.3 V output voltage with 150 mA output current capability to power the system microcontroller (next to some internal logic on VDDD).

The VDD2 regulator needs to be enabled through the digital interface. The default output voltage of VDD2 is 5 V (with 510 mA output current capability), but other output voltages (and corresponding other output current capabilities) can be programmed by the digital interface: 2.5 V, 3.3 V, 7.2 V, 10 V, 12 V, 15 V or 24 V.

#### Bottom Mosfet

The bottom mosfets should have the appropriate drain-source on-resistance and voltage rating ( $\geq$ 80 V) while maintaining low output capacitance, low gate charge and good drain-source diode characteristics (reverse recovery). Preferably, the package(s) should be very small to enable a compact PCB layout as well.

Based on above considerations, it is obvious that dual n-channel mosfet FDC8602 seems to be – by far – the best choice to complement NCL31010.

#### Table 2. DUAL N-CHANNEL MOSFET

| Product | V <sub>DS</sub> (V) | r <sub>DS(on)</sub> (mΩ) | Package Type |

|---------|---------------------|--------------------------|--------------|

| FDC8602 | 100                 | 350                      | TSOT-23-6    |

#### **Switching Frequency**

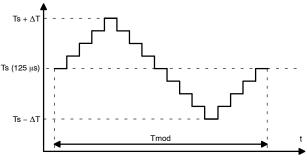

The switching frequency of the NCL31000 DC/DC regulators is 133.3 kHz. This switching frequency is derived from the internal accurate 8 MHz master clock which is divided by 60.

In terms of efficiency and EMI, this low switching frequency is beneficial and yet it allows a small overall solution size (small external inductors and capacitors).

Figure 8. DCDC Block Diagram

#### **Current Sense Resistor and Peak Current Limit**

The inductor current is sensed by a current sense resistor in series with the inductor. The sense resistor value configures the gain of the sensed current signal that is compared to the control voltage to determine when the top mosfet needs to be switched off to maintain regulation. The sense resistor value also configures the peak inductor current limit at which the top mosfet will be switched off – despite a higher control voltage – in order to protect the power stage of the converter against overcurrents.

For the VDD1 regulator, a 750  $m\Omega$  sense resistor is recommended.

For the VDD2 regulator with 5 V output voltage, a 200 m $\Omega$  sense resistor is recommended. For the other output voltages, the recommended sense resistor value can be found in table 6.

The current sense resistors should have a 1% tolerance.

#### Inductor

The inductor saturation current should be higher than the maximum peak switch current of the converter. Within an inductor series, smaller inductance values have a higher saturation current rating. Allowing a larger than typically recommended inductor ripple current enables the use of a physically smaller inductor.

For the VDD1 regulator, a Würth WE–PD Size 7345 Inductor with 390  $\mu$ H Inductance is recommended.

#### Table 3. INDUCTOR FOR VDD1

| Product   | L (μΗ)          | R <sub>DC typ. max.</sub> (Ω) | I <sub>SAT typ.</sub> (A) |

|-----------|-----------------|-------------------------------|---------------------------|

| 744777239 | 390 <u>±20%</u> | 1.25   2.85                   | 0.42                      |

For the VDD2 regulator with 5 V output voltage, the Würth WE–PD Size 1050 P Inductor with 100  $\mu$ H Inductance is recommended. For the other output voltages, the recommended inductance value from the same inductor series can be found in table 6.

#### Table 4. INDUCTORS FOR VDD2

| Product    | L (μΗ)              | R <sub>DC typ. max.</sub> (mΩ) | I <sub>SAT typ.</sub> (A) |

|------------|---------------------|--------------------------------|---------------------------|

| 7447714101 | 100 <sub>±20%</sub> | 165   198                      | 1.8                       |

| 7447714331 | 330 <sub>±20%</sub> | 655   750                      | 1                         |

| 7447714471 | 470 <sub>±20%</sub> | 960   1100                     | 0.82                      |

#### Maximum Output Current

The maximum load current that will be available is the peak inductor current limit minus half the peak-to-peak inductor ripple current:

$$I_{OUT} = I_{LIM} - \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times L \times V_{IN} \times f_{SW}}$$

(eq. 1)

To determine the maximum guaranteed output current above equation should be evaluated with the minimum value of the peak inductor current limit  $I_{LIM}$ , of the inductance L(tolerance and saturation) and of the switching frequency  $f_{SW}$ . For both the VDD1 regulator and all output voltages of the VDD2 regulator, conversely, the maximum value of the input voltage  $V_{IN}$  (i.e. 57 V) should be used here. Likewise for the output voltage  $V_{OUT}$  in above equation an equivalent value  $V_{OUT,eq}$  can be used here to incorporate the slight increase in duty cycle with the output current due to the (maximum) resistance of the (bottom) mosfet, the inductor and the sense resistor:

$$V_{OUT,eq} \left( I_{OUT} \right) = V_{OUT,typ} + \left( r_{DS(on)} + R_{DC} + R_{CS} \right) \times I_{OUT}$$

(eq. 2)

Based on above considerations, the output current capability of both converters operated with the recommended current sense resistance, inductor and bottom mosfet is given below in table 5 and table 6.

#### Table 5. VDD1 CONFIGURATION

| V <sub>OUT</sub> (V) | I <sub>OUT</sub> (mA) | $R_{CS}$ (m $\Omega$ ) | L (µH) |

|----------------------|-----------------------|------------------------|--------|

| 3.3                  | 150                   | 750                    | 390    |

#### Table 6. VDD2 CONFIGURATION

| V <sub>OUT</sub> (V) | I <sub>OUT</sub> (mA) | $R_{CS}$ (m $\Omega$ ) | L (μΗ) |

|----------------------|-----------------------|------------------------|--------|

| 2.5                  | 560                   | 220                    | 100    |

| 3.3                  | 515                   |                        |        |

| 5                    | 510                   | 200                    |        |

| 7.2                  | 415                   |                        | 330    |

| 10                   | 335                   | 330                    | 330    |

| 12                   | 315                   |                        |        |

| 15                   | 285                   |                        |        |

| 24                   | 230                   | 390                    | 470    |

The listed output current capability still contains some headroom for a temporarily higher output current after a load step-up transient (in order not to influence the load transient response settling time) and for the variation of the switching frequency due to spread spectrum modulation.

#### Output Capacitor Selection

The VDD1 and VDD2 regulators do not require any series resistance (ESR) in the output capacitor. Therefore ceramic capacitors with X5R or X7R dielectric are recommended. Unfortunately for these capacitors it is usually not sufficient to only look at the nominal capacitance value: one should always check the Capacitance versus Bias Voltage chart to know the actual remaining capacitance with the output voltage applied!

Some recommended capacitors from the Kemet SMD X5R and X7R series are listed in table 7 (Size 1206) and table 8 (Size 1210).

| Product                          | C <sub>0</sub> (μF) | V <sub>Rated</sub> (V) | C <sub>VDD2</sub><br>(μF @ V) |

|----------------------------------|---------------------|------------------------|-------------------------------|

| C1206C226K9PAC<br>C1206C226M9PAC | 22 ±10%             | 6.3                    | 20.3 @ 2.5                    |

| C1206C226W9PAC                   | 22 <sub>±20%</sub>  |                        | 19 @ 3.3                      |

|                                  |                     |                        | 14.1 @ 5.0                    |

| C1206C106K4PAC                   | 10 <sub>±10%</sub>  | 16                     | 9.9 @ 2.5                     |

|                                  |                     |                        | 9.8 @ 3.3                     |

|                                  |                     |                        | 9.5 @ 5.0                     |

|                                  |                     |                        | 9 @ 7.2                       |

|                                  |                     |                        | 8 @ 10                        |

|                                  |                     |                        | 6.7 @ 12                      |

| C1206C106K3PAC                   | 10 <sub>±10%</sub>  | 25                     | 5.3 @ 15                      |

| C1206C475K5PAC                   | 4.7 <sub>±10%</sub> | 50                     | 3.1 @ 24                      |

Table 7. X5R CAPACITORS SIZE 1206

#### Table 8. X5R AND X7R CAPACITORS SIZE 1210

| Product        | C <sub>0</sub> (μF) | V <sub>Rated</sub> (V) | C <sub>VDD2</sub><br>(μF @ V) |

|----------------|---------------------|------------------------|-------------------------------|

| C1210C107M9PAC | 100 <sub>±20%</sub> | 6.3                    | 79.8 @ 2.5                    |

|                |                     |                        | 60.7 @ 3.3                    |

| C1210C476M9PAC | 47 <u>±20%</u>      | 6.3                    | 42.2 @ 5.0                    |

| C1210C226K8PAC | $22 \pm 10\%$       | 10                     | 17.1 @ 7.2                    |

| C1210C106K4PAC | 10 <sub>±10%</sub>  | 16                     | 8@10                          |

| C1210C106K3RAC | 10 <sub>±10%</sub>  | 25                     | 6.7 @ 15                      |

| C1210C106M6PAC | 10 <sub>±20%</sub>  | 35                     | 9.1 @ 10                      |

|                |                     |                        | 8.7 @ 12                      |

|                |                     |                        | 8 @ 15                        |

|                |                     |                        | 5 @ 24                        |

For X5R and X7R dielectric capacitors the change in capacitance over their operating temperature range is limited to  $\pm 15\%$ .

The output capacitor is needed to stabilize the control loop. The gain crossover frequency of the complex open loop gain can be estimated by:

$$f_{gc} \approx \frac{1}{2 \times \pi \times ACR_p \times C_{VDDx}}$$

(eq. 3)

This gain crossover frequency should be significantly lower than half the switching frequency. This places a constraint on the minimum output capacitance value.

The recommended output capacitors for the VDD1 regulator are listed in Table 9.

#### Table 9. CAPACITOR(S) FOR VDD1

| V <sub>OUT</sub> (V) | C <sub>VDD</sub> Component(s) | C <sub>VDD1</sub> (μF) |

|----------------------|-------------------------------|------------------------|

| 3.3                  | $22~\mu F$ / 6.3 V / 1206     | 19                     |

|                      | $2~x~10~\mu F$ / 16 V / 1206  | 19.6                   |

The minimum output capacitor values for the VDD2 regulator are listed in Table 10 and those listed in bold are recommended.

#### Table 10. CAPACITOR(S) FOR VDD2

| V <sub>OUT</sub><br>(V) | C <sub>VDD</sub> Component(s)                          | C <sub>VDD2</sub><br>(μF) |

|-------------------------|--------------------------------------------------------|---------------------------|

| 2.5                     | 100μF / 6.3V / 1210                                    | 79.8                      |

|                         | 100 $\mu F$ / 6.3 V / 1210 + 22 $\mu F$ / 6.3 V / 1206 | 100.1                     |

| 3.3                     | 100 μF / 6.3 V / 1210                                  | 60.7                      |

|                         | 100 $\mu F$ / 6.3 V / 1210 + 22 $\mu F$ / 6.3 V / 1206 | 79.7                      |

| 5                       | 47 µF / 6.3 V/ 1210                                    | 42.2                      |

|                         | 47 $\mu F$ / 6.3 V / 1210 + 10 $\mu F$ / 16 V / 1206   | 51.7                      |

|                         | 47 $\mu F$ / 6.3 V / 1210 + 22 $\mu F$ / 6.3 V / 1206  | 56.3                      |

| 7.2                     | 22 μF / 10 V / 1210                                    | 17.1                      |

|                         | 2 x 10 µF / 16 V / 1206                                | 18                        |

|                         | 22 $\mu F$ / 10 V / 1210 + 10 $\mu F$ / 16 V / 1206    | 26.1                      |

|                         | 3 x 10 μF / 16 V / 1206                                | 27                        |

| 10                      | 10 μF / 35 V / 1210                                    | 9.1                       |

|                         | 2 x 10 μF / 16 V / 1206                                | 16                        |

| 12                      | 10 μF / 35 V / 1210                                    | 8.7                       |

|                         | 2 x 10 μF / 16 V / 1206                                | 13.4                      |

| 15                      | 10 μF / 35 V / 1210                                    | 8                         |

|                         | 2 x 10 µF / 25 V / 1206                                | 10.6                      |

|                         | 2 x 10 μF / 25 V / 1210                                | 13.4                      |

|                         | 3 x 10 μF / 25 V / 1206                                | 15.9                      |

| 24                      | 10 μF / 35 V / 1210                                    | 5                         |

|                         | 2 x 4.7 μF / 50 V / 1206                               | 6.2                       |

#### **Transient Response**

A first order equivalent circuit of the output impedance of the NCL31000 DC/DC regulators operating in CCM is shown in figure 9.

Figure 9. Model for Loop Response

The output capacitor delivers the initial current for transient loads. The output voltage undershoot/overshoot after a load step up/down transient can be estimated by:

$$\Delta v_{\text{VDDx}} = -\text{ACR}_{p} \times \Delta i_{\text{VDDx}} \tag{eq. 4}$$

On the other hand, the model explains there is a constraint on the maximum output capacitance value. This can be expressed by the damping factor of the parallel RLC circuit:

$$\xi = \frac{1}{2 \times ACR_p} \times \sqrt{\frac{ACL_p}{C_{VDDx}}}$$

(eq. 5)

It is best to keep the damping factor at or above unity. That it is equivalent to keeping the gain crossover frequency at least 4 times higher than the compensation network zero:

$$f_{z} = \frac{ACR_{p}}{2 \times \pi \times ACL_{p}}$$

(eq. 6)

Otherwise the load step response will become oscillatory.

#### **Input Voltage Range**

The minimum input voltage is determined by the NCL31000 VBB undervoltage lockout (UVLO). With appropriate filtering, both the VDD1 and the VDD2 regulators shall continue to operate without interruption in the presence of transients on the DC power supply.

Figure 10. UVLO Filter

Eventually another constraint on the minimum input voltage is related to the subharmonic oscillation phenomenon that might occur in current-mode controlled converters. A rule of thumb is to operate a peak current–mode controller without compensation ramp in CCM up to 33.5% duty cycle in order to keep the  $Q_p$  of the current–mode double pole up to 1.932 ( $\xi_p \ge 0.259$ ). For a peak current–mode controller with compensation ramp in CCM, this rule of thumb for the duty cycle becomes:

$$D \leq \frac{0.335}{\left(1 - \frac{L \times S_X}{V_{OUT}}\right)}$$

(eq. 7)

This duty cycle requirement in CCM can be translated into a minimum input voltage requirement:

$$V_{\rm IN} \ge 2.985 \times (V_{\rm OUT} - L \times S_{\rm X})$$

(eq. 8)

Obviously without compensation ramp this equation simplifies to:

$$V_{\rm IN} \ge 2.985 \times V_{\rm OUT}$$

(eq. 9)

Above constraint explains why a compensation ramp is implemented on the VDD2 regulator for the 15 V and 24 V output voltage settings. Likewise it explains why there is no need for a compensation ramp on the VDD1 regulator and on the VDD2 regulator for the other output voltage settings with an input voltage above 35 V.

The maximum input voltage is determined by the maximum recommended operating voltage of the VBBP pins (i.e. 57 V).

#### **Input Capacitor**

The VBB pin 41 must be decoupled to the source of the bottom mosfets (FDC8602) with a ceramic capacitor. The Kemet X7R Size 1210 Capacitor with 1  $\mu$ F nominal capacitance value is a good option, since the capacitance change over DC bias voltage remains moderate.

| Table 11. ) | X7R CAPACI | FOR SIZE 1210 |

|-------------|------------|---------------|

|-------------|------------|---------------|

| Product        | C <sub>0</sub> (μF) | V <sub>Rated</sub> (V) | C <sub>VPORTP</sub><br>(nF @ V) |

|----------------|---------------------|------------------------|---------------------------------|

| C1210C105K1RAC | 1 <sub>±10%</sub>   | 100                    | 865 @ 41.1                      |

|                |                     |                        | 800 @ 50                        |

|                |                     |                        | 702 @ 57                        |

#### Light Load Operation

In Discontinuous Conduction Mode (DCM), the square of the top mosfet on-time is proportional to the output current. When the load becomes lower than the output current corresponding with the minimum on-time, the converter will exhibit pulse skipping behavior.

#### VDD2 Output voltage

The VDD2 output voltage is programmed in the VDD2\_SEL[2:0] bits of Test Register 10 (&TREG10 0x6E):

#### Table 12.

| Bit [2:0] | VDD2 Output Voltage (V) |

|-----------|-------------------------|

| 000b      | 2.5                     |

| 001b      | 10                      |

| 010b      | 5                       |

| 011b      | 15                      |

| 100b      | 3.3                     |

| 101b      | 12                      |

| 110b      | 7.2                     |

| 111b      | 24                      |

The default output voltage of VDD2 is 5 V.

Do NOT write to Test Register 10 when the VDD2 regulator is already enabled.

#### VDD2 Enable and Shutdown

The VDD2 regulator is enabled when the VDD2\_EN bit in the Control Register (&CTRL 0x04) is set.

#### Table 13.

| Bit 0 | VDD2EN       |

|-------|--------------|

| Ob    | Disable VDD2 |

| 1b    | Enable VDD2  |

#### Soft-Start

Both regulators have soft-start implemented in order to limit the overshoot during start-up.

#### **Short Circuit Protection**

Besides the peak current limit, the NCL31000 contains additional short circuit protection. If the voltage drops significantly below the regulated value during around 15 ms, that specific converter will be shut down. The converter will be automatically restarted after a cool down period of around 120 ms.

#### Severe Faults

The NCL31000 monitors the drain-source voltage of a mosfet that is turned-on: if the voltage becomes too large due to excessive current flow through the mosfet, the respective converter will be latched off.

If this occurs on the VDD2 regulator, the VDD2NOK bit in the Status Positive Register (&STATP) will be set. This will generate an interrupt on the INTB pin if the VDD2NOK bit in the Interrupt Positive Mask Register (&INTP) was not masked.

#### LED DRIVER FUNCTIONAL DESCRIPTION

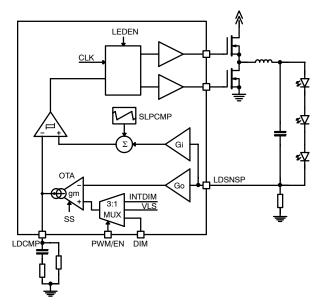

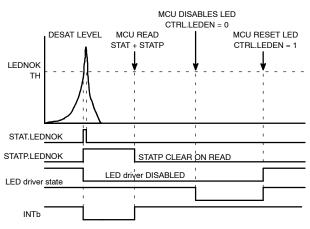

The NCL31000 incorporates a peak current-mode buck LED controller. The controller operates only in CCM mode and is designed to drive high power LED loads up to 90 W and beyond. A block diagram of the concept with the essential parts is given in figure 11.

Figure 11. LED Driver Block Diagram

The LED driver is enabled when the LEDEN bit in the CTRL register is set. When the LED driver is enabled it is switching and regulates a current controlled by the DIMCTRL voltage shown in figure 11. The relationship between DIMCTRL and the LED current is given below.

$$I_{LED} = \frac{(VDIMCTRL - V_{CSA\_0})}{R_{SNS} \times 7.333}$$

(eq. 10)

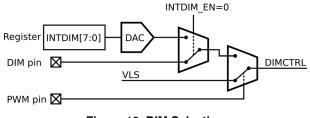

Several sources can be multiplexed to the DIMCTRL signal, see figure 12.

Figure 12. DIM Selection

The analog DIM input gives the best dimming performance in terms of linearity, bandwidth and accuracy.

The DIM pin threshold voltage that provides exactly zero current is the VCSA\_0 voltage. Applying a voltage below the VCSA\_0 lower limit guarantees zero current.

The PWM pin can be used for PWM dimming. A PWM signal on the PWM input can be used to switch the LED

current between zero and the level defined by the voltage level on the DIM pin. The duty-cycle of this signal will define the average LED current. To have a good linear relationship between the duty-cycle and the LED current the frequency of this signal must be below 1 – 2 kHz. This method provides a simple way to use PWM directly to control the LED current, however it does not give the best dimming accuracy and linearity and the duty-cycle range is limited. When the PWM digital input pin is low, the MUX connects VLS to DIMCTRL. VLS has a steady value just below VCSA\_0 to guarantee that the LED driver is regulating zero current when PWM = 0. When the PWM pin is high, the voltage on the DIM pin is connected to DIMCTRL.

When the INTDIMEN bit in the INTDIM register is set the internal 7-bit DAC output is connected to DIMCTRL. In this case, the LED current will depend on the value programmed in the 7 bits of the INTDIM register. The relationship between the register value and the DAC output voltage is given below.

$$V_{\text{INTDIM}} = \frac{V_{\text{REF}} \times (\text{INTDIM}[7:0] + 1)}{128} \tag{eq. 11}$$

The internal DAC can be useful when, for example, the host MCU is being re-flashed and the DIM voltage is not controlled during this period. In this case the MCU can instruct the internal DAC to take control of DIMCTRL net moments before the MCU firmware is under maintenance. This is called 'Warm Boot'.

#### Voltage Reference

The NCL31000 provides a precise ( $\pm 0.3\%$ ) 2.4 V reference voltage on the VREF pin, which can be used by external components, for example, as the reference of an external PWM to DIM circuit or a DAC that controls the DIM pin voltage. The load on this pin must be limited to 2 mA to ensure the accuracy of the voltage. The advantage of using this VREF is that the VREF voltage and the VCSA\_0 voltage (the threshold point for zero current) are related. If VREF deviates, VCSA\_0 will deviate in the same direction by a proportional factor, thus the LED current regulation inaccuracy of a circuit that is VREF based does not suffer from the VREF deviation.

#### **Sense Resistor**

Select an appropriate sense resistor based on the maximum LED current. The resistor value can be calculated according to:

$$R_{S} = \frac{(VREF - VCSA_{0})}{7.333 \times IIed_{max}}$$

(eq. 12)

Make sure to select a sense resistor that has a value between 50 m $\Omega$  and 300 m $\Omega$ . Consider the power rating and the accuracy. A 1 W or 2 W / 1% sense resistor is sufficient for most applications.

#### **Buck Inductor**

The rule of thumb is to choose the inductor so that the peak-peak current ripple in the inductor is 20...30% of the max dc-current. Calculate the required inductance according to:

$$L = \frac{Vi}{4 \times fs \times Iled_{max} \times 0.3}$$

(eq. 13)

Make sure that the specified RMS current rating of the inductor (typically the current that results in a temperature increase of 40°C due to copper losses) is at or above the max dc-current used in the application. The saturation current rating minus 20% derating should still be at or above the largest peak current. Use the formulas below to find appropriate minimum RMS current and saturation current values.

$$Ir_{max-pkpk} = \frac{Vi_{max}}{4 \times fs \times L}$$

(eq. 15)

$$lsat > \left( lledmax + \frac{lr_{max-pkpk}}{2} \right) \times 1.2$$

(eq. 16)

#### **Output Capacitor**

The purpose of the output capacitor is to filter the high frequency inductor ripple current to some extent. This must be a 100 V rated ceramic capacitor(s) with low ESR. The required output capacitor depends on the switching frequency, the expected LED ripple current ( $Ir_{LED-pkpk}$ ), the dynamic resistance of the LED string (Rd) and the inductor ripple current ( $Ir_{max-pkpk}$ ). The expression is given below:

$$C_{O} = \frac{8}{\pi^{2}} \times \frac{lr_{max-pkpk}}{2\pi \times fs \times lr_{LED} \times Rd}$$

(eq. 17)

Substituting Irmax gives:

$$C_{O} = \frac{Vi_{max}}{31 \times fs^{2} \times L \times Ir_{LED-pkpk} \times Rd}$$

(eq. 18)

A reasonable output capacitor value would be anything between 100 nF and  $1 - 3 \mu$ F. Try to avoid 1608 (metric) packages or smaller to avoid audible noise. The output capacitance has no significant effect on stability.

#### **Bandwidth & Stability**

The control loop in this configuration exhibits no poles to be compensated in the bandwidth area so a single compensation capacitor connected to LDCMP pin will suffice. This strategy is suitable for a bandwidth up to  $1/10^{\text{th}}$ of the switching frequency and provides a phase margin of 60 - 75 degrees. The compensation capacitor can be calculated as:

$$C_{C} = 2.44 \times \frac{G_{M}}{2 \times \pi \times f_{C}}$$

(eq. 19)

$f_C$  is the wanted cross-over frequency and  $G_M = 1$  mS.

#### **Slope Compensation**

Since a peak–current–mode buck convertor is sensitive to sub–harmonic oscillations for duty–cycles above 33% slope compensation must be added. There is a minimum amount of slope needed to damp sub–harmonic oscillations within one switching cycle. The slope value can be programmed in the SLPCMP register. The default value is a good setting for most applications and normally no changes have to be made to this register. If the phase margin is not sufficient (<60 degrees), program '0' to SLP1 and SLP2 field in the SLPCMP register.

The required amount of slope increases with output voltage and the ratio from output to input voltage (duty-cycle). A separate slope setting can be programmed for slopes below 50% duty-cycle (SLP1 field) and above (SLP2 field). The possibilities for SLP1 and SLP2 fields are presented in table 14 and 15 respectively. The default value for SLP1 and SLP2 is set to 0.1 V/µs and 0.3 V/µs. Increase SLP1 one level if sub-harmonic oscillation is seen below 50% duty-cycle. Increase SLP2 one level if subharmonic oscillation is seen above 50% duty-cycle.

Table 14. SLP1 VALUES

| SPL1 Register Value | Slope [V/µs] |

|---------------------|--------------|

| 0                   | 0.1          |

| 1                   | 0.2          |

| 2                   | 0.3          |

| 3                   | 0.4          |

| SPL2 Register Value | Slope [V/µs] |

|---------------------|--------------|

| 0                   | 0.3          |

| 1                   | 0.4          |

| 2                   | 0.6          |

| 3                   | 0.9          |

#### **Switching Frequency**

All the clocks in the chip are derived from a main 8 MHz clock. The LED driver's switching frequency can be programmed with the LEDFC register. The value in the register relates to the LED driver switching frequency clock according to table 16. The default switching frequency is 500 kHz. For most applications that regulate LED currents below 1.5 A, a switching frequency of 500 kHz is a good choice. For applications that regulate above 1.5 A, 400 kHz is recommended.

| LEDFC [5:0] | DIVISOR | LED_CLK [kHz] |  |  |

|-------------|---------|---------------|--|--|

| 0           | 8       | 1000.00       |  |  |

| 1           | 10      | 800.00        |  |  |

| 2           | 12      | 666.67        |  |  |

| 3           | 14      | 571.43        |  |  |

| 4           | 16      | 500.00        |  |  |

| 5           | 18      | 444.44        |  |  |

| 6           | 20      | 400.00        |  |  |

| 7           | 22      | 363.64        |  |  |

| 8           | 24      | 333.33        |  |  |

| 9           | 26      | 307.69        |  |  |

| 10          | 28      | 285.71        |  |  |

| 11          | 32      | 250.00        |  |  |

| 12          | 34      | 235.29        |  |  |

| 13          | 38      | 210.53        |  |  |

| 14          | 42      | 190.48        |  |  |

| 15          | 46      | 173.91        |  |  |

| 16          | 52      | 153.85        |  |  |

| 17          | 56      | 142.86        |  |  |

| 18          | 64      | 125.00        |  |  |

| 19          | 70      | 114.29        |  |  |

| 20          | 76      | 105.26        |  |  |

| 21          | 84      | 95.24         |  |  |

| 22          | 102     | 78.43         |  |  |

| 23          | 112     | 71.43         |  |  |

| 24          | 124     | 64.52         |  |  |

| 25          | 150     | 53.33         |  |  |

| 26          | 180     | 44.44         |  |  |

#### Table 16. SWITCHING FREQUENCY

#### **Switching Transistors**

The selection of the switching transistors is a critical aspect for the correct functioning of the LED driver. It can significantly impact the power efficiency and thermal performance. The top fet in particular will dissipate most of the switching losses. Because this component is essential to the LED driver performance it is advised to select one of the validated transistors for top and bottom given in table 17. The transistors are ranked high–low for efficiency. The typical LED driver efficiency achievable with the proposed transistors for 30 – 70 W range is 97%. The best combination is to use FDMA037N08L as bottom fet and NVTFS6H880N or NVTFS6H888N as top fet.

#### Table 17. TRANSISTOR SELECTION

|        | Product      | V <sub>DS</sub> (V) | r <sub>DS(on)</sub> (mΩ) |

|--------|--------------|---------------------|--------------------------|

| Тор    | NVTFS6H880N  | 80                  | 32                       |

|        | NVTFS6H888N  | 80                  | 55                       |

|        | NVTFS6H860N  | 80                  | 21.1                     |

| Bottom | FDMA037N08LC | 80                  | 36.5                     |

Do not use external gate resistors for the transistors. The chip uses the voltages at the gate nodes as feedback for desaturation protection and fast switching.

#### **Thermal Considerations**

Additional copper is needed for good thermal performance. A typical design with LED currents below 2 A (<60 W) requires a small (both copper sides) cooling plane with size  $2 - 3 \text{ cm}^2$  connected to the drain of the top fet. For 2 A and above (>60 W), a  $3 - 4 \text{ cm}^2$  copper plane is recommended on both sides. The bottom fet drain connection should also have a small  $0.5 - 1 \text{ cm}^2$  copper plane.

#### Metrology

The NCL31000 incorporates a high accuracy metrology block that measures several voltages, currents and temperatures in the system. This is made possible by an internal 10–bit ADC, which is multiplexed to measure VBB, VDD11, VDD2, VLED, ILED, IBB, IVDD1, IVDD2 and TLED. The metrology measurements can be enabled with the DIAG\_EN bit in the CTRL register. The measurements are referenced to GND and are sampled every 100 ms. The measurements can be read out from the 16–bit registers. The relationship between the measured voltage/current/temperature and the values read in the registers is given below.

$$VBB = VBB_{reg} \times \frac{5000}{201} \times \frac{VREF}{2^{16}}$$

(eq. 20)

$$IBB = IBB_{reg} \times \frac{VREF}{6 \times Rs \times 2^{16}}$$

(eq. 21)

$$VDD = VDD_{reg} \times \frac{3}{2} \times \frac{VREF}{2^{16}}$$

(eq. 22)

$$VDD2 = VDD2_{reg} \times \frac{30}{4} \times \frac{VREF}{2^{16}}$$

(eq. 23)

$$IDD = IDD_{reg} \times \frac{VREF}{10 \times Rs \times 2^{16}}$$

(eq. 24)

$$\mathsf{IDD2} = \mathsf{IDD2}_{\mathsf{reg}} \times \frac{\mathsf{VREF}}{\mathsf{10} \times \mathsf{Rs} \times \mathsf{2^{16}}} \tag{eq. 25}$$