# 38 V, 1.5 A synchronous step-down converter with low quiescent current

SO<sub>8</sub>L

#### **Maturity status link**

L6981

#### **Features**

- 3.5 V to 38 V operating input voltage

- Output voltage from 0.85 V to V<sub>IN</sub>

- 1.5 A DC output current

- Internal compensation network

- Two different versions: LCM for high efficiency at light-loads and LNM for noise sensitive applications

- 2 μA shutdown current

- Internal soft-start

- Enable

- Overvoltage protection

- · Output voltage sequencing

- Thermal protection

- Synchronization to external clock for LNM devices

- SO8 package

# **Applications**

- Designed for 24 V buses industrial power systems

- · 24 V battery powered equipment

- Decentralized intelligent nodes

- · Sensors and always-on applications

- Low noise applications

## **Description**

The L6981 is an easy to use synchronous monolithic step-down regulator capable of delivering up to 1.5 A DC to the load. The wide input voltage range makes the device suitable for a broad range of applications. The L6981 is based on a peak current mode architecture and is packaged in an SO8 with internal compensation, thus minimizing design complexity and size.

The L6981 is available both in low consumption mode (LCM) and low noise mode (LNM) versions. LCM maximizes the efficiency at light-load with controlled output voltage ripple so the device is suitable for battery-powered applications. LNM makes the switching frequency constant and minimizes the output voltage ripple for light-load operations, meeting the specification for low noise sensitive applications.

The EN pin provides enable/disable functionality. The typical shutdown current is  $2~\mu A$  when disabled. As soon as the EN pin is pulled up the device is enabled and the internal 1.3 ms soft-start takes place. Pulse-by-pulse current sensing on both power elements implements an effective constant current protection and thermal shutdown prevents thermal run-away.

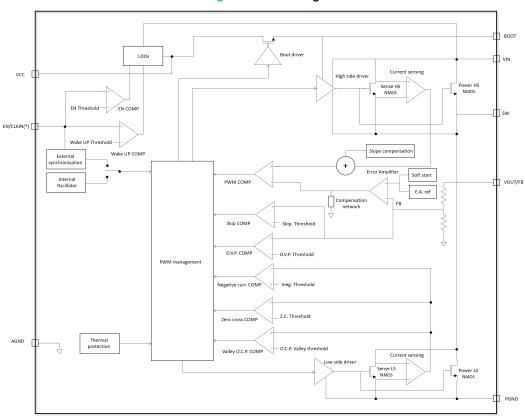

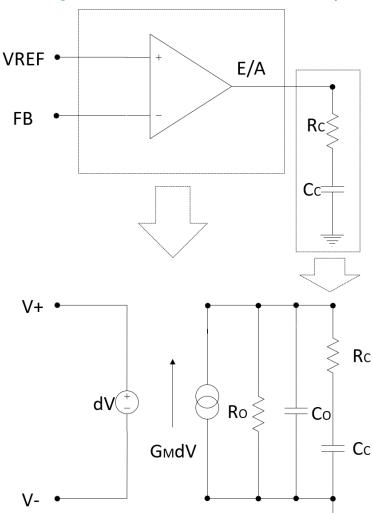

# 1 Diagram

Figure 1. Block diagram

(\*) Synchronization is allowed for LNM versions only.

DS13554 - Rev 1 page 2/49

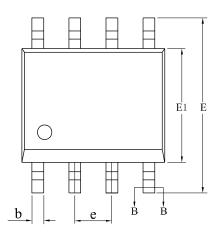

# 2 Pin configuration

SW 1 8 PGND

BOOT 2 7 VIN

VCC 3 6 AGND

FB/VOUT 4 5 EN/CLKIN(\*)

Figure 2. Pin connection (top view)

(\*) Synchronization is allowed for LNM versions only.

**Table 1. Pin description**

| Pin # | Symbol   | Function                                                                                                                                                                                         |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SW       | Switching node                                                                                                                                                                                   |

| 2     | воот     | Connect an external capacitor (100 nF typ.) between BOOT and SW pins. The gate charge required to drive the internal NMOS is refreshed during the low side switch conduction time.               |

| 3     | VCC      | This pin supplies the embedded analog circuitry. Connect a ceramic capacitor ( $\geq$ 1 µF) to filter internal voltage reference.                                                                |

| 4     | FB/VOUT  | FB is output voltage sensing with eternal voltage divider                                                                                                                                        |

| 5     | EN/CLKIN | Enable pin with internal voltage divider. Pull down/up to disable/enable the device.  In LNM versions, this pin is also used to provide an external clock signal, which synchronizes the device. |

| 6     | AGND     | Analog ground                                                                                                                                                                                    |

| 7     | VIN      | DC input voltage                                                                                                                                                                                 |

| 8     | PGND     | Power ground                                                                                                                                                                                     |

DS13554 - Rev 1 page 3/49

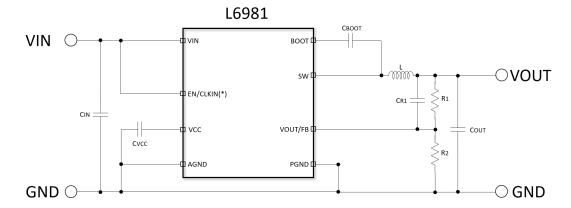

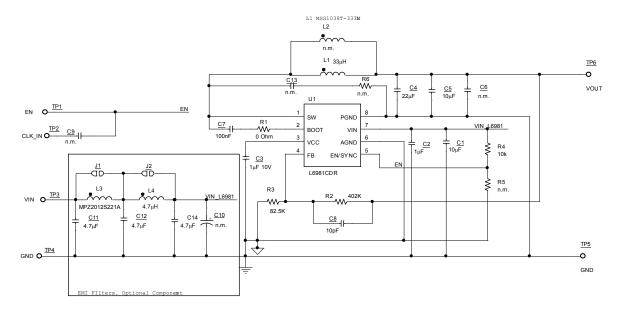

# 3 Typical application circuit

Figure 3. Basic application (adjustable version)

(\*) Synchronization is allowed for LNM versions only.

Table 2. Typical application components

| Symbol            | Value  | Description                 |

|-------------------|--------|-----------------------------|

| C <sub>IN</sub>   | 10 μF  | Input capacitor             |

| C <sub>VCC</sub>  | 1 μF   | VCC bypass capacitor        |

| C <sub>BOOT</sub> | 100 nF | Bootstrap capacitor         |

| C <sub>OUT</sub>  | 22 µF  | Output capacitor            |

| R <sub>1</sub>    | 400 kΩ | VOUT divider upper resistor |

| R <sub>2</sub>    | 82 kΩ  | VOUT divider lower resistor |

| L                 | 33 μΗ  | Output inductor             |

DS13554 - Rev 1 page 4/49

# 4 Absolute maximum ratings

Stressing the device above the ratings listed in the table below may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Table 3. Absolute maximum ratings

| Symbol         | Parameter                               | Min.            | Max.                    | Unit |

|----------------|-----------------------------------------|-----------------|-------------------------|------|

| VIN            | Maximum pin voltage                     | -0.3            | 42                      | V    |

| PGND to AGND   | Maximum pin voltage                     | -0.3            | 0.3                     | V    |

| BOOT           | Maximum pin voltage                     | SW - 0.3        | SW + 4                  | V    |

| VCC            | Maximum pin voltage                     | -0.3            | Min. (VIN + 0.3 V; 4 V) | V    |

| VOUT/FB        | Maximum pin voltage                     | -0.3            | 8                       | V    |

| EN             | Maximum pin voltage                     | -0.3            | VIN + 0.3               | V    |

| SW             | Maximum pin valtaga                     | -0.85           | VIN + 0.3               | V    |

| Svv            | Maximum pin voltage                     | -3.9 for 0.5 ns | VIN + 0.3               | V    |

| IHS, ILS       | High-side / Low-side RMS switch current |                 | 1.5                     | Α    |

| T <sub>J</sub> | Operating temperature range             | -40             | 150                     | °C   |

| TSTG           | Storage temperature range               | -65             | 150                     | °C   |

| TLEAD          | Lead temperature (soldering 10 sec.)    |                 | 260                     | °C   |

Note: All values are referred to AGND unless otherwise specified.

**Table 4. ESD performance**

| Symbol | Parameter              | Test conditions | Value | Unit |

|--------|------------------------|-----------------|-------|------|

| ESD    | ESD Protection voltage | НВМ             | 2     | kV   |

| ESD    | ESD Protection voltage | CDM pins        | 500   | V    |

Table 5. Thermal data

| Symbol            | Parameter                                                                                           | Value | Unit |

|-------------------|-----------------------------------------------------------------------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal resistance junction ambient (device soldered on the STMicroelectronics demonstration board) | 65    | °C/W |

DS13554 - Rev 1 page 5/49

# **5** Electrical characteristics

Table 6. Electrical characteristics T $_{\rm J}$  = 25 °C, V $_{\rm IN}$  = 24 V unless otherwise specified.

| Symbol                   | Parameter                                              | Test Conditions                                                         | Min.  | Тур.  | Max.  | Unit |

|--------------------------|--------------------------------------------------------|-------------------------------------------------------------------------|-------|-------|-------|------|

| V <sub>IN</sub>          | Operating input voltage range                          |                                                                         | 3.5   |       | 38    | V    |

| V <sub>INH</sub>         | V <sub>CC</sub> rising threshold                       |                                                                         | 2.3   |       | 3.3   | V    |

| V <sub>INL</sub>         | V <sub>CC UVLO</sub> falling threshold                 |                                                                         | 2.15  |       | 3.15  | V    |

| I <sub>PK</sub> (1)      | Dools assessed limit                                   | No slope contribution                                                   | 2     | 2.3   |       | Α    |

| IPK (''                  | Peak current limit                                     | Full slope contribution                                                 | 1.55  | 1.8   |       | Α    |

| $I_{VY}$                 | Valley current limit                                   |                                                                         | 1.7   | 2     | 2.3   | Α    |

| I <sub>SKIP</sub> (1)(2) | Skip current limit                                     |                                                                         |       | 0.35  |       | Α    |

| I <sub>VY_SINK</sub> (1) | Reverse current limit                                  | LNM or VOUT overvoltage                                                 | 1.25  | 1.5   | 1.75  | Α    |

| R <sub>DSON_HS</sub>     | High-side RDSON                                        |                                                                         |       | 0.175 |       | Ω    |

| R <sub>DSON_LS</sub>     | Low-side RDSON                                         |                                                                         |       | 0.125 |       | Ω    |

| F <sub>SW</sub>          | Switching frequency                                    |                                                                         | 360   | 400   | 440   | KHz  |

| T <sub>OFF_MIN</sub>     | Minimum OFF time                                       |                                                                         |       | 185   |       | ns   |

| T <sub>ON_MIN</sub>      | Minimum ON time                                        |                                                                         |       | 85    |       | ns   |

| Enable                   |                                                        |                                                                         |       | 1     |       |      |

|                          | Wakeup threshold                                       | Rising                                                                  |       |       | 0.7   | V    |

| V <sub>WAKE_UP</sub>     |                                                        | Falling                                                                 | 0.2   |       |       | V    |

| Vev                      | Finable threshold  Rising 1.08  Hysteresis             | Rising                                                                  | 1.08  | 1.2   | 1.32  | V    |

| V EN                     |                                                        |                                                                         | 0.2   |       | V     |      |

| VCC regulator            |                                                        |                                                                         |       |       |       |      |

| $V_{CC}$                 | LDO output voltage                                     |                                                                         | 3.0   | 3.3   | 3.6   | V    |

| Power consun             | nption                                                 |                                                                         |       |       |       |      |

| I <sub>SHTDWN</sub>      | Shutdown current from V <sub>IN</sub>                  | EN = GND                                                                |       | 2     | 3     | μA   |

| LCM Device               |                                                        |                                                                         |       |       |       |      |

| $I_{Q\_OPVIN}$           | Quiescent current from V <sub>IN</sub>                 |                                                                         | 20    | 35    | 60    | μA   |

| LNM Device               |                                                        |                                                                         |       |       |       |      |

| $I_{Q\_OPVIN}$           | Quiescent current from VIN                             |                                                                         | 1.6   | 2.3   | 3     | mA   |

| Soft start               |                                                        |                                                                         |       |       |       |      |

| T <sub>SS</sub>          | Internal soft-start                                    |                                                                         | 1     | 1.3   | 1.6   | ms   |

| Error amplifier          | •                                                      |                                                                         |       |       |       |      |

|                          |                                                        | Adjustable version T <sub>J</sub> = 25 °C                               | 0.845 | 0.85  | 0.855 | V    |

| $V_{FB}$                 | Voltage feedback Adjustable version                    | 0.042                                                                   |       | 0.050 | .,    |      |

|                          |                                                        | $T_J = -40  ^{\circ}\text{C} \le T_J \le 125  ^{\circ}\text{C}  ^{(3)}$ | 0.842 | 0.85  | 0.858 | V    |

| Overvoltage p            | rotection                                              |                                                                         |       |       |       |      |

| V <sub>OVP</sub>         | Overvoltage trip (V <sub>OVP</sub> /V <sub>REF</sub> ) |                                                                         | 115   | 120   | 125   | %    |

| V <sub>OVP_HYST</sub>    | Overvoltage Hysteresis                                 |                                                                         | 1     | 2     | 6     | %    |

DS13554 - Rev 1 page 6/49

| Symbol                    | Parameter                                                                 | Test Conditions | Min. | Тур. | Max. | Unit |  |

|---------------------------|---------------------------------------------------------------------------|-----------------|------|------|------|------|--|

| Synchronizatio            | Synchronization (LNM versions only)                                       |                 |      |      |      |      |  |

| f <sub>CLKIN</sub> (4)    | Synchronization range                                                     |                 | 200  |      | 500  | KHz  |  |

| V <sub>CLKIN_TH</sub> (4) | Amplitude of synchronization clock                                        |                 | 2.3  |      |      | V    |  |

|                           | Synchronization pulse ON and OFF time 2.3 ≤ V <sub>CLKIN_TH</sub> ≤ 2.5 V |                 | 60   |      |      | ns   |  |

| V <sub>CLKIN_T</sub> (4)  | Synchronization pulse ON and OFF time V <sub>CLKIN_TH</sub> > 2.5 V       |                 | 20   |      |      | ns   |  |

| Thermal Shutdown          |                                                                           |                 |      |      |      |      |  |

| T <sub>SHDWN</sub> (5)    | Thermal shutdown temperature                                              |                 |      | 165  |      | °C   |  |

| T <sub>HYS</sub> (5)      | Thermal shutdown hysteresis                                               |                 |      | 30   |      | °C   |  |

Parameter tested in the static condition during testing phase. The parameter value may change over a dynamic application condition.

- 2. LCM version.

- 3. Specifications in the 40 to 125 °C temperature range are assured by characterization and statistical correlation.

- 4. LNM version.

- 5. Not tested in production.

DS13554 - Rev 1 page 7/49

# 6 Functional description

The L6981 device is based on a "peak current mode", constant frequency control. Therefore, the intersection between the error amplifier output and the sensed inductor current generates the PWM control signal to drive the power switch.

The device features LNM (low noise mode) that implements a forced PWM control, or LCM (low consumption mode) to increase the efficiency at light-load.

The main internal blocks shown in the block diagram in Figure 1 are:

- · Embedded power elements

- The ramp for the slope compensation to avoid subharmonic instability

- A transconductance error amplifier with integrated compensation network

- The high-side current sense amplifier to sense the inductor current

- · A "Pulse Width Modulator" (PWM) comparator and the driving circuitry of the embedded power elements

- The soft-start block ramps up the reference voltage on error amplifier, thus decreasing the inrush current at power-up. The EN pin inhibits the device when driven low

- The EN/CLK pin section, which for LNM versions, allows synchronizing the device to an external clock generator

- The pulse-by-pulse high-side / low-side switch current sensing to implement the constant current protection

- A circuit to implement the thermal protection function

- The OVP circuitry to discharge the output capacitor in case of overvoltage event.

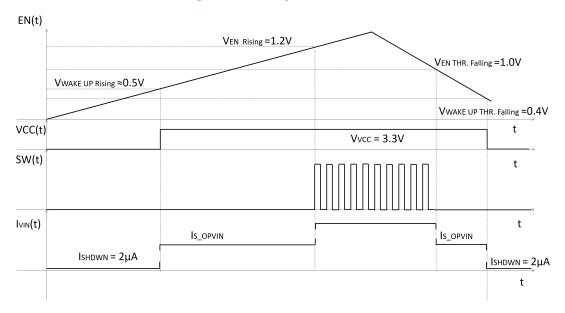

#### 6.1 Enable

The EN pin is a digital input that turns the device on or off.

In order to maximize both the EN threshold accuracy and the current consumption, the device implements two different thresholds:

- 1. The Wake-Up threshold,  $V_{WAKE\ UP} = 0.5\ V$  (see Table 6)

- 2. The Start-Up threshold, V<sub>EN</sub> = 1.2 V (see Table 6)

The following image shows the device behavior.

Figure 4. Power up/down behavior

DS13554 - Rev 1 page 8/49

When the voltage applied on the EN pin rises over  $V_{WAKEUP, RISING}$ , the device powers up the internal circuit increasing the current consumption.

As soon as the voltage rises over the  $V_{EN,\;RISING}$ , the device starts the switching activities as described in Section 6.2 Soft-start.

Once the voltage becomes lower than  $V_{\text{EN,FALLING}}$ , the device interrupts the switching activities.

As soon as the voltage becomes lower than  $V_{WAKEUP,FALLING}$ , the device powers down the internal circuit reducing the current consumption.

The pin is VIN compatible.

Please refer to Table 6 for the reported thresholds.

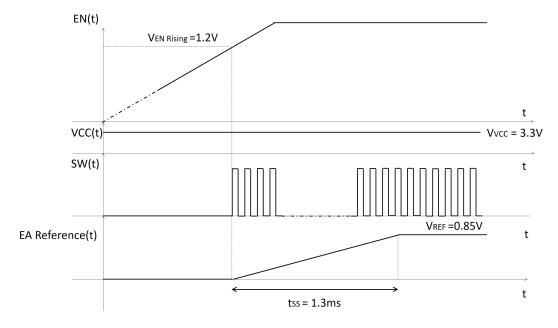

#### 6.2 Soft-start

The soft-start (SS) limits the inrush current surge and makes the output voltage increase monotonically. The device implements the soft-start phase ramping the internal reference with very small steps. Once the SS ends, the Error Amplifier reference is switched to the internal value of 0.85 V coming directly from the band gap cell

Figure 5. Soft-start procedure

During normal operation, a new soft-start cycle takes place in case of:

- 1. Thermal shutdown event

- 2. UVLO event

- 3. EN pin rising over VEN threshold. Please refer to Table 6.

DS13554 - Rev 1 page 9/49

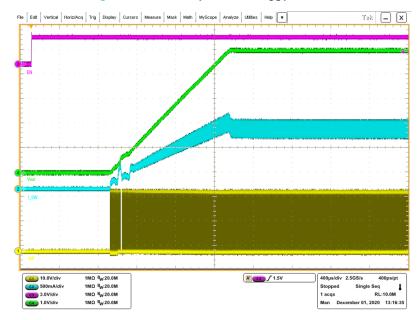

Figure 6. Soft-start phase with  $I_{OUT} = 1.25 A$

## 6.3 Undervoltage lockout

The device implements the undervoltage lockout (UVLO) continuously sensing the voltage on the VCC pin, if the UVLO lasts more than 10 µs, the internal logic resets the device by turning off both LS and HS.

After the reset, if the EN pin is still high, the device repeats the soft-start procedure.

## 6.4 Light-load operation

The L6981 implements two different light-load strategies:

- 1. Low consumption mode (LCM).

- Low noise mode (LNM).

Please refer to Table 11 to select the part number with the preferred light-load strategy.

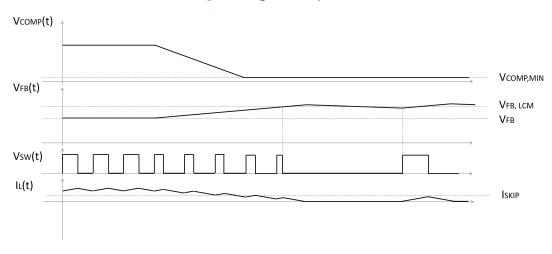

## 6.4.1 Low consumption mode (LCM)

The LCM maximizes the efficiency at light-load.

When the switch peak current request is lower than the  $I_{SKIP}$  threshold (please refer to Electrical characteristics table), the device regulates  $V_{OUT}$  by the skip threshold. The minimum voltage is given by:

$$V_{OUT, LCM} = V_{FB, LCM} \cdot \frac{R_{PH} + R_{PL}}{R_{PL}} \tag{1}$$

Where  $V_{FB, LCM}$  is 1.8% (typ.) higher than  $V_{FB}$ .

The device interrupts the switching activities when two conditions happen together:

- 1. The peak inductor current required is lower than I<sub>SKIP</sub>.

- 2. The voltage on the FB pin is higher than V<sub>FB, LCM</sub>.

DS13554 - Rev 1 page 10/49

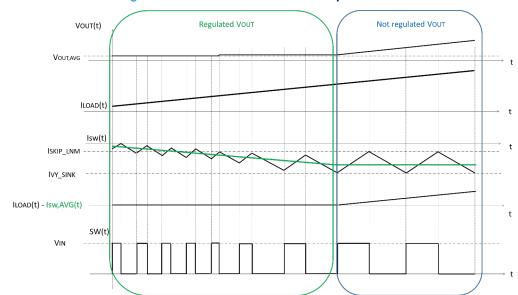

Figure 7. Light-load operation

A new switching cycle takes place once the voltage on the FB pins becomes lower than  $V_{\text{FB,LCM}}$ .

The HS switch is kept on until the inductor current reaches I<sub>SKIP</sub>.

Once the current on the HS reaches the defined value, the device turns the HS off and turns the LS on. The LS is kept enabled until one of the following conditions occurs:

- 1. The inductor current sensed by the LS becomes equal to zero.

- 2. The switching period ends.

If, at the end of the switching cycle, the voltage on the FB pin rises over the V<sub>FB,LCM</sub> threshold, the LS is kept enabled until the inductor current becomes equal to zero. Otherwise, the device turns on the HS again and starts a new switching pulse.

During the burst pulse, if the energy transferred to  $C_{OUT}$  increases the VFB level over the threshold defined in Equation 1, the device interrupts the switching activities. The new cycle takes place only when VFB becomes lower than the defined threshold. Otherwise, as soon as the LS is turned off, the HS is turned on.

Given the energy stored in the inductor during a burst, the voltage ripple depends on the capacitor value:

$$V_{OUT\;RIPPLE} = \frac{\Delta Q_{IL}}{C_{OUT}} = \frac{\int_0^{T_{BURST}} (I_L(t))dt}{C_{OUT}} \tag{2}$$

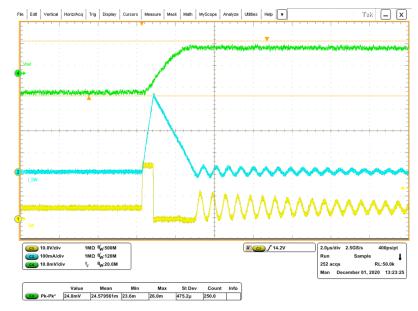

Figure 8. LCM operation with I<sub>SKIP</sub> = 350 mA typ. at zero load. L = 33  $\mu$ H; C<sub>OUT</sub> = 32  $\mu$ F

DS13554 - Rev 1 page 11/49

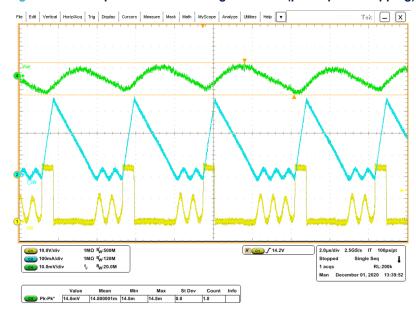

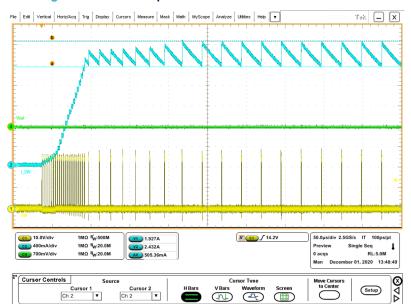

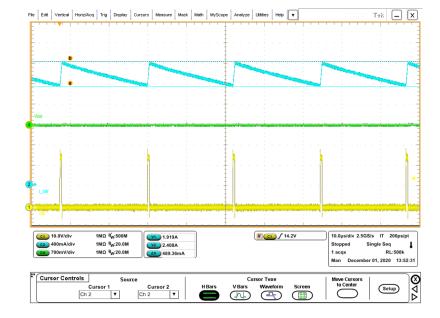

Figure 9. LCM operation over loading condition (part 1-pulse skipping)

Value

Mean

Min

Max

St Dev

Count

Info

CS

Pk-Pk\*

26.0mV

26.000002m

26.0m

26.0m

0.0

1.0

1.0

DS13554 - Rev 1 page 12/49

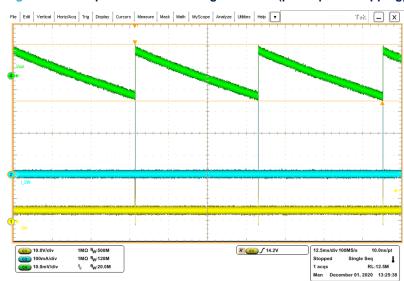

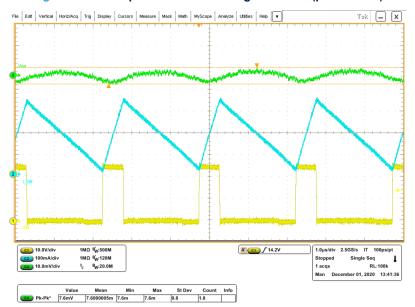

Figure 11. LCM operation over loading condition (part 3-pulse skipping)

DS13554 - Rev 1 page 13/49

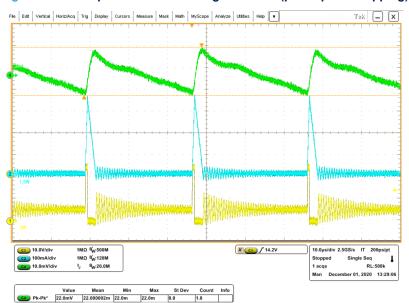

#### 6.4.2 Low noise mode (LNM)

The low noise mode implements a forced PWM operation over the different loading conditions. The LNM features a constant switching frequency to minimize the noise in the final application and a constant voltage ripple at fixed VIN

The regulator in steady loading condition operates in continuous conduction mode (CCM) over the different loading conditions.

The triangular shape current ripple (with zero average value) flowing into the output capacitor gives the output voltage ripple, that depends on the capacitor value and the equivalent resistive component (ESR). Consequently, the output capacitor has to be selected in order to have a voltage ripple compliant with the application requirements.

$$V_{OUT\;RIPPLE} = ESR \cdot \Delta I_{LMAX} + \frac{\Delta I_{LMAX}}{8 \cdot C_{OUT} \cdot f_{SW}} \tag{3}$$

Usually the resistive component of the ripple can be neglected if the selected output capacitor is a multi-layer ceramic capacitor (MLCC).

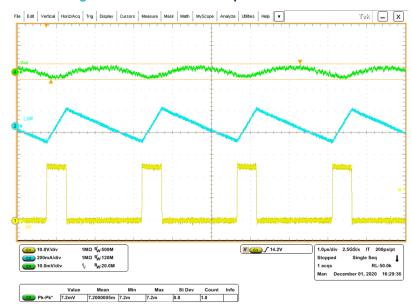

Figure 13. Low noise mode operation at zero load

DS13554 - Rev 1 page 14/49

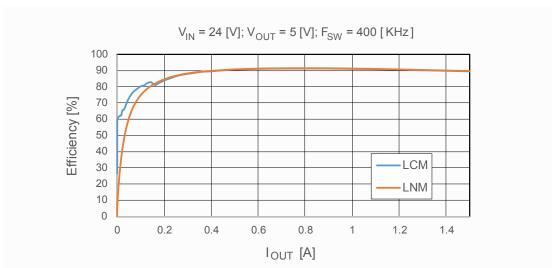

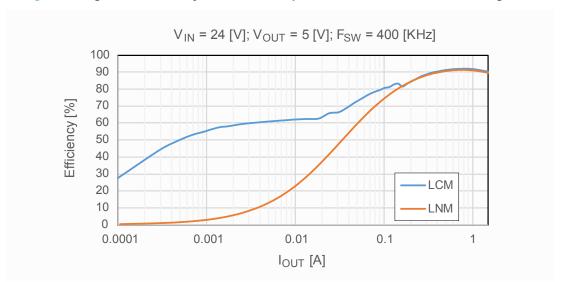

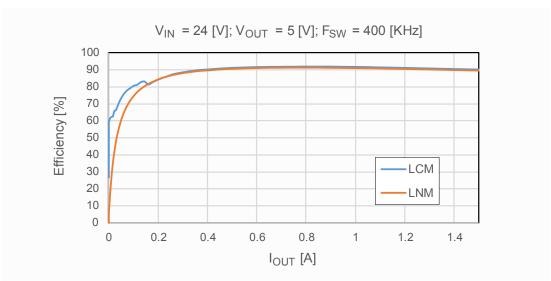

### 6.4.3 Efficiency for Low consumption mode and Low noise mode part number

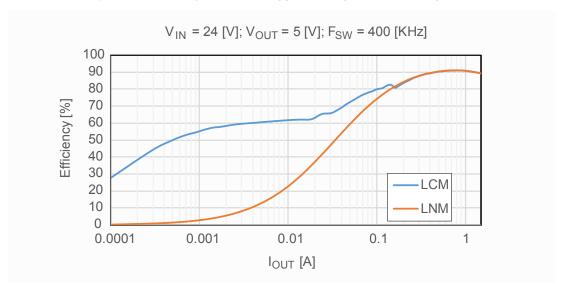

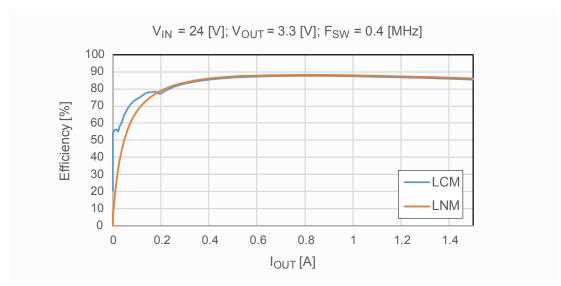

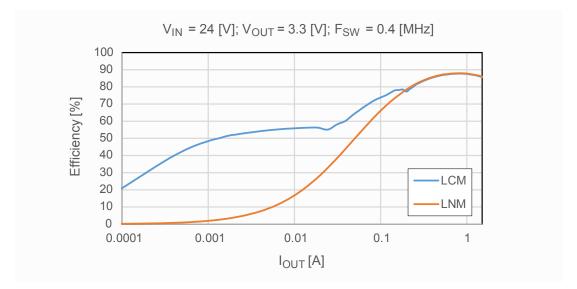

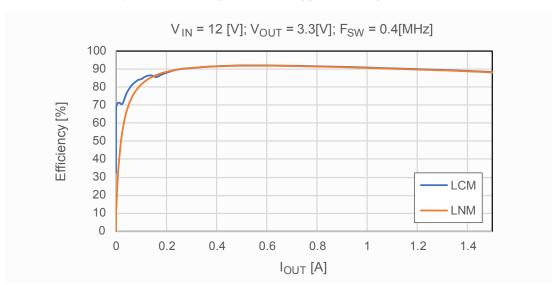

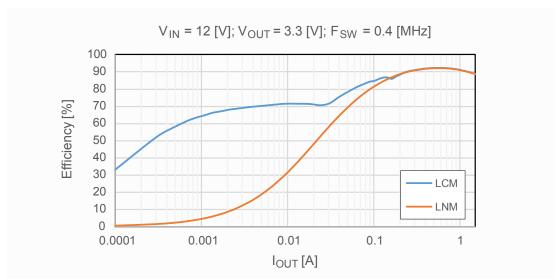

Figure 14 and Figure 15 report the efficiency measurements to highlight the gap at the light-load between LNM and LCM part numbers. The graph reports also the same efficiency at the medium / high load.

Figure 14. Light-load efficiency for low consumption mode and low noise mode - linear scale

DS13554 - Rev 1 page 15/49

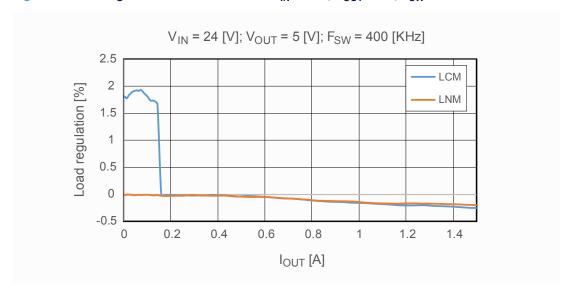

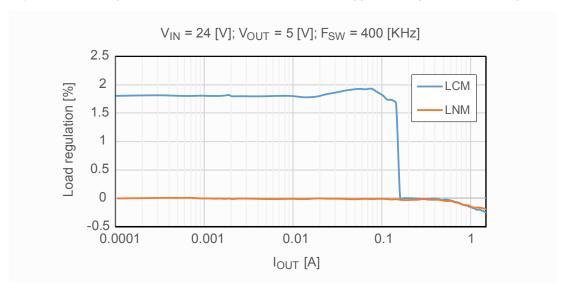

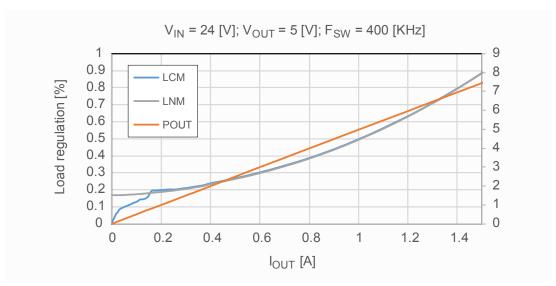

#### 6.4.4 Load regulation for low consumption mode and low noise mode part number

Figure 16 and Figure 17 report the load regulation to highlight the gap, given by the different regulation strategy, at the light-load between LNM and LCM part numbers. When the required I<sub>OUT</sub> is higher than the threshold defined in the Low consumption mode (LCM) paragraph, the behavior of the different part numbers is the same.

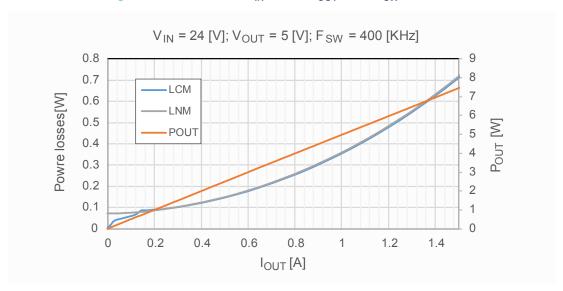

Figure 16. Load regulation for LCM and LNM.  $V_{IN}$  = 24 V;  $V_{OUT}$  = 5 V;  $F_{SW}$  = 400 KHz - linear scale

Figure 17. Load regulation for low noise mode.  $V_{IN}$  = 24 V;  $V_{OUT}$  = 5 V;  $F_{SW}$  = 400 KHz - log scale

## 6.5 Overvoltage protection

The overvoltage is a second level protection, and it should never be triggered in normal operating conditions if the system is properly dimensioned. In other words, the selection of the external power components and the dynamic performance determined by the compensation network should guarantee an output voltage regulation within the overvoltage threshold even during the worst-case scenario in terms of load transitions. The protection is reliable and able to operate even during normal load transitions for a system whose dynamic performance is not in line with the load dynamic request. Consequently, the output voltage regulation would be affected.

DS13554 - Rev 1 page 16/49

### 6.5.1 Low consumption mode part number

The overvoltage protection continuously compares the FB pin with 120% nominal output voltage and enables the low-side MOSFET at the beginning of the switching cycle keeping it active until 1.5 A typ. negative current limitation is reached, in order to discharge the output capacitor.

The following graph shows the LCM part number behavior during an OVP event.

Figure 18. OVP event low consumption mode part number

As soon as the output voltage goes out of the OVP hysteresis (typ. 2%) the L6981 device sets the switching node on high impedance. It restarts the switching activity accordingly with the main loop regulation of the peak current mode architecture.

DS13554 - Rev 1 page 17/49

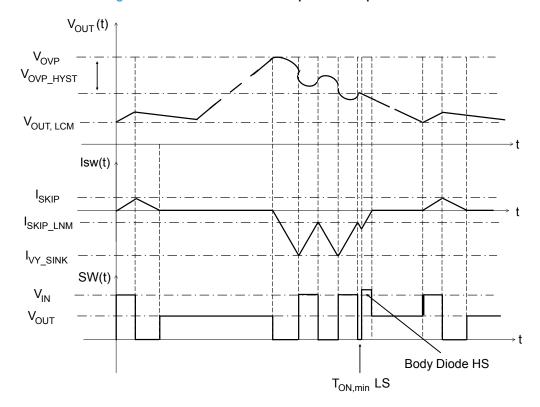

#### 6.5.2 Low noise mode part number

The following graph shows the LNM part number behavior during an OVP event.

Figure 19. OVP event low noise mode part number

The LNM device regulates the output voltage with valley sinking capability down to the negative current limitation (IVY\_SINK in Figure OVP Event Low Noise Mode part number). This hysteretic operating mode between peak current mode threshold (ISKIP\_LNM) and modulated low side switch conduction time for VOUT regulation persists until the valley current level triggers the negative current limitation (IVY\_SINK), that is the maximum sinking capability of the device (highlighted in green in Figure 19).

If the source injection further increases, the output voltage is a partitioning between source impedance and maximum sinking capability above described (highlighted in blue in Figure 19).

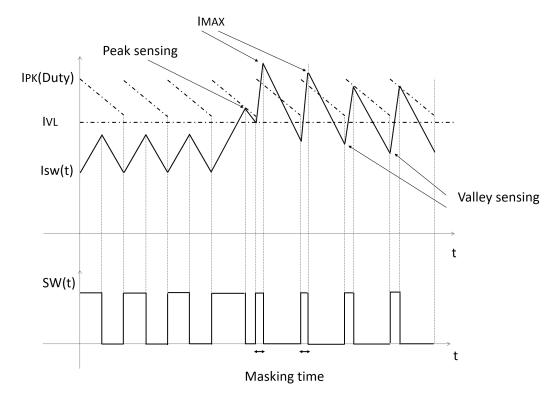

#### 6.6 Overcurrent protection

The current protection circuitry features a constant current protection, so the device limits the maximum peak current (please refer to Table 6) in an overcurrent condition.

The L6981 device implements a pulse-by-pulse current sensing on both power elements (high-side and low-side switches) for effective current protection over the duty cycle range. The high-side current sensing is called "peak", the low-side sensing "valley".

The internal noise generated during the switching activity makes the current sensing circuitry ineffective for a minimum conduction time of the power element. This time is called "masking time" because the information from the analog circuitry is masked by the logic to prevent an erroneous detection of the overcurrent event. Therefore, the peak current protection is disabled for a masking time after the high-side switch is turned on. The masking time for the valley sensing is activated after the low-side switch is turned on. In other words, the peak current protection can be ineffective at extremely low duty cycles, the valley current protection at extremely high duty cycles.

The L6981 device assures an effective overcurrent protection sensing the current flowing in both power elements. In case one of the two current sensing circuitries is ineffective because of the masking time, the device is protected, sensing the current on the opposite switch. Thus, the combination of the "peak" and "valley" current limits assure the effectiveness of the overcurrent protection even in extreme duty cycle conditions.

DS13554 - Rev 1 page 18/49

In case the current diverges because of the high-side masking time, the low-side power element is turned on until the switch current level drops below the valley current sense threshold. The low-side operation is able to prevent the high-side turn-on, so the device can skip pulses decreasing the switching frequency.

Figure 20. Overcurrent protection behavior

In a worst case scenario, reported in Figure 20 of the overcurrent protection, the switch current is limited to:

$$I_{MAX} = I_{VY} + \frac{V_{IN} - V_{OUT}}{L} \cdot T_{MASKHS} \tag{4}$$

Where IVY is the current threshold of the valley sensing circuitry (please refer to Electrical characteristics table) and  $T_{MASKHS}$  is the masking time of the high-side switch.

In most of the overcurrent conditions, the conduction time of the high-side switch is higher than the masking time and so the peak current protection limits the switch current.

$$I_{MAX} = I_{PEAKTH} \tag{5}$$

The DC current flowing in the load in overcurrent condition is:

$$I_{DCOUT} = I_{MAX} - \frac{I_{RIPPLE}(V_{OUT})}{2} = I_{MAX} - \left(\frac{V_{IN} - V_{OUT}}{2 \cdot L} \cdot T_{ON}\right) \tag{6}$$

DS13554 - Rev 1 page 19/49

Figure 21 shows the L6981 soft-start procedure with V<sub>OUT</sub> shorted to GND.

Figure 21. Soft-start procedure with VOUT shorted to GND

Figure 22 shows the L6981 over current protection with a persistent short-circuit between V<sub>OUT</sub> and GND.

Figure 22. Over current procedure with persistent short circuit between V<sub>OUT</sub> and GND

#### 6.7 Thermal shutdown

The shutdown block disables the switching activity if the junction temperature is higher than a fixed internal threshold ( $T_{SHDWN}$  refer to Table 6). The thermal sensing element is close to the power elements, ensuring fast and accurate temperature detection. A hysteresis of approximately 30 °C prevents the device from turning ON and OFF too fast. After a thermal protection event has expired, the L6981 restarts with a new soft-start.

DS13554 - Rev 1 page 20/49

# 7 Closing the loop

The following image shows the typical compensation network required to stabilize the system.

VIN PWM control Current sense LC Resistor divider HS filter switch Ins/gcs LS Соит switch FΒ RLOAD Compensation network VREF PWM comparator  $R_2$ RcError amplifier

Figure 23. Block diagram of the loop

## 7.1 GCO(s) control to output transfer function

The accurate control to output transfer function for a buck peak current mode converter can be written as:

$$G_{CO}(s) = R_{LOAD} \cdot g_{CS} \cdot \frac{1}{1 + \frac{R_{LOAD} \cdot T_{SW}}{L} \cdot \left[ m_C \cdot (1 - D) - 0.5 \right]} \cdot \frac{\left( 1 + \frac{s}{\omega_Z} \right)}{\left( 1 + \frac{s}{\omega_P} \right)} \cdot F_H \left( s \right)$$

(7)

Where  $R_{LOAD}$  represents the load resistance,  $g_{CS}$  the equivalent sensing trans-conductance of the current sense circuitry,  $\omega_P$  the single pole introduced by the power stage and  $\omega_Z$  the zero given by the ESR of the output capacitor.  $F_H$  (s) accounts the sampling effect performed by the PWM comparator on the output of the error amplifier that introduces a double pole at one half of the switching frequency.

$$\omega_Z = \frac{1}{ESR \cdot C_{OUT}} \tag{8}$$

$$\omega_P = \frac{1}{R_{LOAD} \cdot C_{OUT}} + \frac{m_C \cdot (1 - D) - 0.5}{L \cdot C_{OUT} \cdot f_{SW}}$$

(9)

Where:

$$m_{C} = 1 + \frac{S_{e}}{S_{n}}$$

$$S_{e} = I_{SLOPE} \cdot f_{SW}$$

$$S_{n} = \frac{V_{IN} - V_{OUT}}{I}$$

(10)

Where I<sub>SLOPE</sub> is equal to 1 A.

$S_n$  represents the ON time slope of the sensed inductor current,  $S_e$  the ON time slope of the external ramp that implements the slope compensation to avoid sub-harmonic oscillations at duty cycle over 50 %.

The sampling effect contribution F<sub>H</sub> (s) is:

DS13554 - Rev 1 page 21/49

$$F_H(s) = \frac{1}{1 + \frac{s}{\omega_n \cdot Q_P} + \frac{s^2}{\omega_n^2}} \tag{11}$$

Where:

$$Q_P = \frac{1}{\pi \cdot [m_C \cdot (1 - D) - 0.5]} \tag{12}$$

## 7.2 Error amplifier compensation network

The following figure shows the typical compensation network required to stabilize the system.

Figure 24. Trans-conductance embedded error amplifier

RC and CC introduce a pole and a zero in the open loop gain. The transfer function of the error amplifier and its compensation network is:

$$A_O(s) = \frac{A_{VO} \cdot (1 + s \cdot R_C \cdot C_C)}{s^2 \cdot R_O \cdot C_O \cdot R_C \cdot C_C + s \cdot (R_O \cdot C_C + R_O \cdot C_O + R_C \cdot C_C) + 1}$$

$$\tag{13}$$

Where:

$$A_{VO} = G_m \cdot R_O \tag{14}$$

The poles of this transfer function are (if  $C_C \gg C_O$ ):

DS13554 - Rev 1 page 22/49

$$f_{PLF} = \frac{1}{2 \cdot \pi \cdot R_O \cdot C_C} \tag{15}$$

$$f_{PHF} = \frac{1}{2 \cdot \pi \cdot R_O \cdot C_O} \tag{16}$$

Whereas the zero is defined as:

$$f_Z = \frac{1}{2 \cdot \pi \cdot R_C \cdot C_C} \tag{17}$$

## 7.3 Voltage divider

The contribution of a simple voltage divider is:

$$G_{DIV}(s) = \frac{R_2}{R_1 + R_2} \tag{18}$$

A small signal capacitor in parallel to the upper resistor (only for the adjustable part number) of the voltage divider implements a leading network ( $f_{ZERO} < f_{POLE}$ ), sometimes necessary to improve the system phase margin:

Figure 25. Leading network example

(\*) Synchronization is allowed for LNM versions only. Laplace transformer of the leading network:

$$G_{DIV}(s) = \frac{R_2}{R_1 + R_2} \cdot \frac{(1 + s \cdot R_1 \cdot C_{R1})}{\left(1 + s \cdot \frac{R_1 \cdot R_2}{R_1 + R_2} \cdot C_{R1}\right)} \tag{19}$$

$$f_Z = \frac{1}{2 \cdot \pi \cdot R_1 \cdot C_{R1}} \tag{20}$$

$$f_P = \frac{1}{2 \cdot \pi \cdot \frac{R_1 \cdot R_2}{R_1 + R_2} \cdot C_{R1}} \tag{21}$$

$$f_Z < f_P \tag{22}$$

So closing the loop, the loop gain is:

$$G(s) = G_{DIV}(s) \cdot G_{CO}(s) \cdot A_O(s)$$

(23)

DS13554 - Rev 1 page 23/49

# 8 Design of the power components

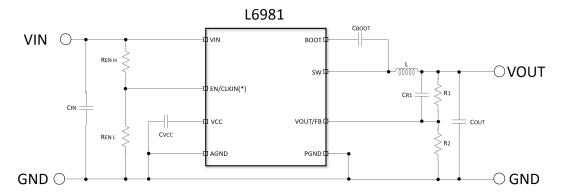

### 8.1 Programmable power up threshold

The Enable rising threshold is equal to 1.2 V typical (refer to Table 6). The power up threshold is adjusted accordingly with the following equation:

$$V_{Power\ Up} = 1.2 \cdot \left(1 + \frac{R_{EN\ H}}{R_{EN\ L}}\right) \tag{24}$$

Figure 26. Leading network example

(\*) Synchronization is allowed only for LNM versions.

The Enable falling threshold is equal to 1.0 V typical (refer to Electrical characteristics table). The turn off threshold is obtained accordingly with the following equation:

$$V_{Power\ Down} = 1.0 \cdot \left(1 + \frac{R_{EN\ H}}{R_{EN\ L}}\right) \tag{25}$$

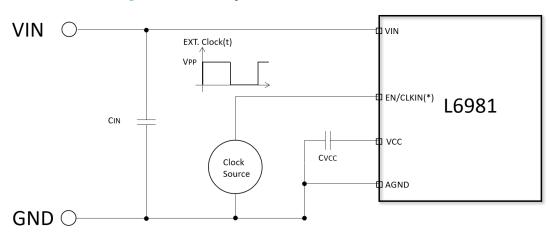

## 8.2 External synchronization (only available for Low Noise Mode)

The device allows a direct connection between a clock source and the EN/CLKIN pin.

Figure 27. External synchronization. Direct connection

(\*) Synchronization is allowed only for LNM versions.

DS13554 - Rev 1 page 24/49

The device internally implements a low pass filter connected to EN/CLKIN pin that is able to acquire the average value of the applied signal.

The device turns on when the average of the signal applied is higher than  $V_{EN}$  rising (refer to Table 6). The device turns off when the average of the signal should be lower than  $V_{EN}$  falling (refer to Table 6).

Considering, for example, a clock source with  $V_{PP}$  = 5.0 V, the minimum duty cycle to guarantee the power-up is given by:

$$Duty_{min} = \frac{V_{EN,TH\,Rising}}{V_{PP}} = 0.24 \tag{26}$$

The maximum duty cycle to guarantee the turn off is given by:

$$Duty_{MAX,} = \frac{V_{EN,TH Falling}}{V_{PP}} = 0.2$$

(27)

The device allows also the AC coupling.

CEN

CEN

CEN

CIDCK

Source

CIOCK

Source

CIOCK

Source

CIOCK

Source

CIOCK

Source

CIOCK

Source

CIOCK

Source

CVCC

C

Figure 28. External synchronization. AC coupling

(\*) Synchronization is allowed only for LNM versions.

The AC-coupling allows the device to keep the power-up and down thresholds defined by the partition connected to the EN/CLKIN pin and described in the "Programmable power up threshold" section.

The following table resumes the minimum pulse duration and maximum duty cycle that allow the synchronization, keeping the selected power-up and down thresholds.

| V <sub>PP</sub> [V] | T <sub>ON,MIN</sub> [ns] | D <sub>MAX</sub> [%] |

|---------------------|--------------------------|----------------------|

| 2.3                 | 70                       | 45                   |

| 3.3                 | 20                       | 30                   |

| 5                   | 20                       | 20                   |

Table 7. External synchronization AC coupling suggested operation range

The minimum amplitude for the external clock signal is, for both configurations, equal to 2.3 V.

The network given by  $C_{EN}$  and  $R_{ENL}$  sets a high pass filter. Considering a resistor in the order of 220 K $\Omega$ , a capacitor equal to 1 nF is a correct choice.

### 8.3 Output voltage adjustment

The error amplifier reference voltage is 0.85 V typical (refer to Table 6). The output voltage is adjusted accordingly with the following equation:

DS13554 - Rev 1 page 25/49

$$V_{OUT} = 0.85 \cdot \left(1 + \frac{R_1}{R_2}\right) \tag{28}$$

CR1 capacitor is sometimes useful to increase the small signal phase margin (please refer to Section 7 Closing the loop)

Figure 29. Application circuit

(\*) Synchronization is allowed only for LNM versions.

## 8.4 Design of the power components

#### 8.4.1 Input capacitor selection

The input capacitor voltage rating must be higher than the maximum input operating voltage of the application. During the switching activity a pulsed current flows into the input capacitor and so, its RMS current capability must be selected accordingly with the application conditions. Internal losses of the input filter depend on the ESR value, so usually low ESR capacitors (like multilayer ceramic capacitors) have higher RMS current capability. On the other hand, given the RMS current value, lower ESR input filter has lower losses and so contributes to higher conversion efficiency.

The maximum RMS input current flowing through the capacitor can be calculated as:

$$I_{RMS} = I_{OUT} \cdot \sqrt{\left(1 - \frac{D}{\eta}\right) \cdot \frac{D}{\eta}} \tag{29}$$

Where  $I_{OUT}$  is the maximum DC output current, D is the duty cycles,  $\eta$  is the efficiency. This function has a maximum at D = 0.5 and, considering  $\eta$  = 1, it is equal to  $I_{OUT}/2$ . In a specific application, the range of possible duty cycles has to be considered in order to find out the maximum RMS input current. The maximum and minimum duty cycles can be calculated as:

$$D_{MAX} = \frac{V_{OUT} + \Delta V_{LOWSIDE}}{V_{INmin} + \Delta V_{LOWSIDE} - \Delta V_{HIGHSIDE}}$$

(30)

$$D_{min} = \frac{V_{OUT} + \Delta V_{LOWSIDE}}{V_{INMAX} + \Delta V_{LOWSIDE} - \Delta V_{HIGHSIDE}}$$

(31)

Where  $\Delta V_{HIGHSIDE}$  and  $\Delta V_{LOWSIDE}$  are the voltage drops across the embedded switches. The peak-to-peak voltage across the input filter can be calculated as:

$$V_{PP} = \frac{I_{OUT}}{C_{IN} \cdot F_{SW}} \cdot \left(1 - \frac{D}{\eta}\right) \cdot \frac{D}{\eta} + ESR \cdot \left(I_{OUT} + \Delta I_L\right)$$

(32)

In case of negligible ESR (MLCC capacitor), the equation of  $C_{IN}$  as a function of the target  $V_{PP}$  can be written as follows:

$$C_{IN} = \frac{I_{OUT}}{V_{PP} \cdot F_{SW}} \cdot \left(1 - \frac{D}{\eta}\right) \cdot \frac{D}{\eta} \tag{33}$$

DS13554 - Rev 1 page 26/49

Considering  $\eta = 1$  this function has its maximum in D = 0.5:

$$C_{INmin} = \frac{I_{OUT}}{4 \cdot V_{PPMAX} \cdot F_{SW}} \tag{34}$$

Typically,  $C_{IN}$  is dimensioned to keep the maximum peak-to-peak voltage across the input filter in the order of 5 %  $V_{INMAX}$ .

In the following table, some suitable capacitor part numbers are listed.

**Table 8. Input capacitors**

| Manufacturer | Series               | Size | Cap value (μF) | Rated voltage (V) |

|--------------|----------------------|------|----------------|-------------------|

| TDK          | CGA5L3X5R1H106K160AB | 1206 | 10             | 50                |

|              | C3216X5R1H106K160AB  | 1206 | 10             | 50                |

| Murata       | GRT31CR61H106KE01    | 1206 | 10             | 50                |

#### 8.4.2 Inductor selection

The inductor current ripple flowing into the output capacitor determines the output voltage ripple. Usually the inductor value is selected in order to keep the current ripple lower than 20% - 40% of the output current over the input voltage range. The inductance value can be calculated by the following equation:

$$\Delta I_L = \frac{V_{IN} - V_{OUT}}{L} \cdot T_{ON} = \frac{V_{OUT}}{L} \cdot T_{OFF} \tag{35}$$

Where  $T_{ON}$  and  $T_{OFF}$  are the ON and OFF time of the internal power switch. The maximum current ripple, at fixed  $V_{OUT}$ , is obtained at maximum  $T_{OFF}$  that is at minimum duty cycle. So fixing  $\Delta I_L$  = 20% to 40% of the maximum output current, the minimum inductance value can be calculated:

$$L_{min} = \frac{V_{OUT}}{\Delta IL_{MAX}} \cdot \frac{1 - D_{min}}{F_{SW}} \tag{36}$$

For those applications requiring higher inductor value for minimized current ripple, pay attention as the maximum value must prevent the sub-harmonic instability given the designed internal slope compensation. As a consequence the inductor value must satisfy the quality factor range:

$$0.4 \le Q_P \le 1.33 \tag{37}$$

Where QP has been defined in Section 7.1 GCO(s) control to output transfer function. The peak current through the inductor is given by:

$$I_{L,PK} = I_{OUT} + \frac{\Delta I_L}{2} \tag{38}$$

So if the inductor value decreases, the peak current (that has to be lower than the current limit of the device) increases. The higher the inductor value, the higher the average output current that can be delivered, without reaching the current limit.

#### 8.4.3 Output capacitor selection

The triangular shaped current ripple (with zero average value) flowing into the output capacitor gives the output voltage ripple, which depends on the capacitor value and the equivalent resistive component (ESR). Therefore, the output capacitor has to be selected in order to have a voltage ripple compliant with the application requirements.

The voltage ripple equation can be calculated as:

$$\Delta V_{OUT} = ESR \cdot \Delta I_{L,MAX} + \frac{\Delta I_{L,MAX}}{8 \cdot C_{OUT} \cdot F_{SW}}$$

(39)

For a ceramic (MLCC) capacitor, the capacitive component of the ripple dominates the resistive one. While for an electrolytic capacitor the opposite is true. Neglecting the ESR contribution, the minimum value of the output capacitor is given by:

DS13554 - Rev 1 page 27/49

$$C_{OUT,min,RIPPLE} = \frac{\Delta I_{L,MAX}}{8 \cdot \Delta V_{OUT} \cdot F_{SW}} \tag{40}$$

As the compensation network is internal, the output capacitor should be selected in order to have a proper phase margin and then a stable control loop. A good rule to obtain a proper dimensioning for the minimum amount of the output capacitor is to set the target system bandwidth equal to  $F_{SW}/10$ . The following equation takes into account the precedent consideration:

$$C_{OUT,BW,min} = \frac{8.04}{\frac{F_{SW}}{10} \cdot V_{OUT}} \tag{41}$$

The maximum amount of the output capacitor is given by:

$$C_{OUT,BW,min} = \frac{1.38 \cdot 10^{-4}}{V_{OUT}} \tag{42}$$

DS13554 - Rev 1 page 28/49

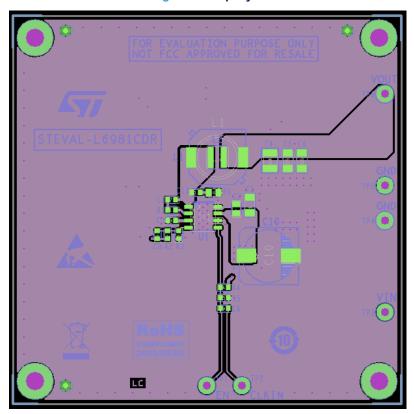

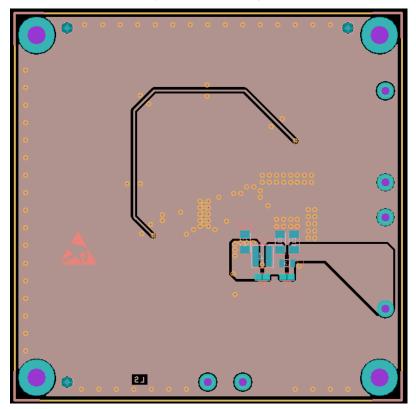

# 9 Application board

The figure below shows the reference evaluation board schematic:

Figure 30. Evaluation board schematic

The additional input filter (C11, L3, C12, L4, C14 and C10) limits the conducted emission on the power supply.

DS13554 - Rev 1 page 29/49

Table 9. Bill of material

| Reference     | Part number          | Description    | Manufacturer       |

|---------------|----------------------|----------------|--------------------|

| C1            | C3216X7R1H106K160AC  | 10 μF          | TDK                |

| C2            | CGA4J3X7R1H105K125AB | 1 μF           | TDK                |

| C3            |                      | 1 μF           |                    |

| C4            | GRJ32EC71E226KE11    | 22 μF          | Murata             |

| C6            |                      | n.m.           |                    |

| C5            | C3216X7R1H106K160AC  | 10 μF          | TDK                |

| C7            |                      | 100 nF         |                    |

| C8            |                      | 10 pF          |                    |

| C9            |                      | n.m.           |                    |

| C10           |                      | n.m.           |                    |

| C11, C12, C14 | GRM31CR71H475KA12    | 4.7 μF         | Murata             |

| C13           |                      | n.m.           |                    |

| L1            | MSS1038T-333ML       | 33 μΗ          | Coilcraft          |

| L2            |                      | n.m.           |                    |

| L3            | MPZ2012S221AT000     | 220 Ω, 100 MHz | TDK                |

| L4            | XAL4030-472ME        | 4.7 µH         | Coilcraft          |

| R1            |                      | 0 Ω            |                    |

| R2            |                      | 402 kΩ         |                    |

| R3            |                      | 82.5 kΩ        |                    |

| R4            |                      | 10 kΩ          |                    |

| R5            |                      | n.m.           |                    |

| R6            |                      | n.m.           |                    |

| U1            | L6981                |                | STMicroelectronics |

DS13554 - Rev 1 page 30/49

Figure 32. Bottom layer

DS13554 - Rev 1 page 31/49

# 10 Efficiency curves

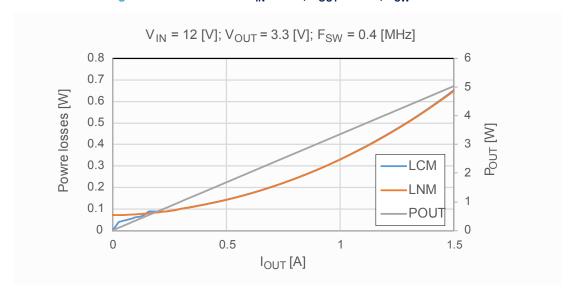

The following three figures show the efficiency and power losses acquired on the standard evaluation board of the device, selecting the following output filter:

- COUT:

- 1 x GRJ32EC71E226KE11 22 μF 16 V (Murata)

- 1 x C3216X7R1H106K160AC 10 μF 50 V (TDK)

- Inductor:

- MSS1038T-333ML (Coilcraft)

- C8:

- 10 pF

Figure 33. Efficiency  $V_{IN}$  = 24 V;  $V_{OUT}$  = 5 V;  $F_{SW}$  = 0.4 MHz

Figure 34. Efficiency  $V_{IN}$  = 24 V;  $V_{OUT}$  = 5 V;  $F_{SW}$  = 0.4 MHz (log scale)

DS13554 - Rev 1 page 32/49

Figure 35. Power losses  $V_{IN}$  = 24 V;  $V_{OUT}$  = 5 V;  $F_{SW}$  = 0.4 MHz

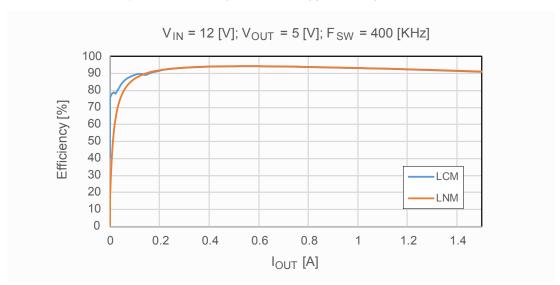

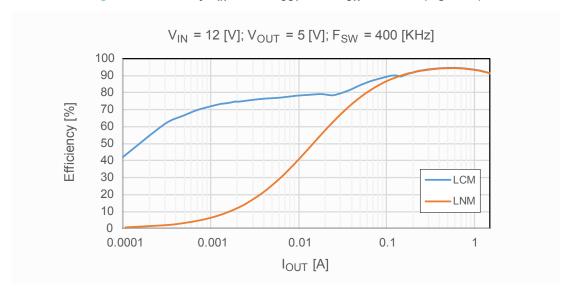

The following three figures show the efficiency and power losses acquired on the standard evaluation board of the device, selecting the following output filter:

- COUT:

- 1 x GRJ32EC71E226KE11 22 μF 16 V (Murata)

- 1 x C3216X7R1H106K160AC 10 μF 50 V (TDK)

- Inductor:

- MSS1038T-333ML (Coilcraft)

- C8:

- 10 pF

Figure 36. Efficiency V<sub>IN</sub> = 12 V; V<sub>OUT</sub> = 5 V; F<sub>SW</sub> = 0.4 MHz

DS13554 - Rev 1 page 33/49

Figure 37. Efficiency  $V_{IN}$  = 12 V;  $V_{OUT}$  = 5 V;  $F_{SW}$  = 0.4 MHz (log scale)

Figure 38. Power losses  $V_{IN} = 12 \text{ V}$ ;  $V_{OUT} = 5 \text{ V}$ ;  $F_{SW} = 0.4 \text{ MHz}$

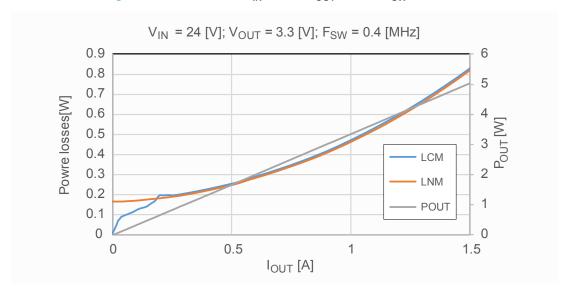

The following three figures show the efficiency and power losses acquired on the standard evaluation board of the device, selecting the following output filter:

- COUT:

- 1 x GRJ32EC71E226KE11 22 μF 16 V (Murata)

- 1 x C3216X7R1H106K160AC 10 μF 50 V (TDK)

- Inductor:

- MSS1038T-223ML (Coilcraft)

- C8:

- 10 pF

DS13554 - Rev 1 page 34/49

Figure 39. Efficiency  $V_{IN}$  = 24 V;  $V_{OUT}$  = 3.3 V; FSW = 0.4 MHz

DS13554 - Rev 1 page 35/49

Figure 41. Power losses  $V_{IN}$  = 24 V;  $V_{OUT}$  = 3.3 V;  $F_{SW}$  = 0.4 MHz

The following three figures show the efficiency and power losses acquired on the standard evaluation board of the device, selecting the following output filter:

- COUT:

- 1 x GRJ32EC71E226KE11 22 μF 16 V (Murata)

- 1 x C3216X7R1H106K160AC 10 μF 50 V (TDK)

- Inductor:

- MSS1038T-223ML (Coilcraft)

- C8:

- 10 pF

Figure 42. Efficiency V<sub>IN</sub> = 12 V; V<sub>OUT</sub> = 3.3 V; F<sub>SW</sub> = 0.4 MHz

DS13554 - Rev 1 page 36/49

Figure 43. Efficiency  $V_{IN}$  = 12 V;  $V_{OUT}$  = 3.3 V;  $F_{SW}$  = 0.4 MHz (log scale)

DS13554 - Rev 1 page 37/49

### 11 Thermal dissipation

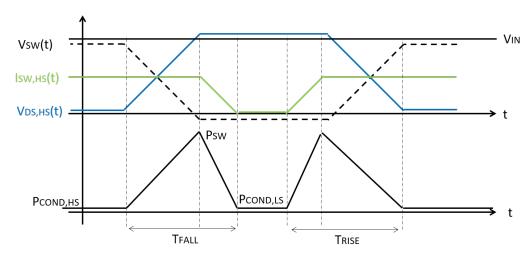

The thermal design is important in order to prevent thermal shutdown of the device if junction temperature goes above 165°C. The three different sources of losses within the device are:

Conduction losses due to the ON resistance of the high-side switch (R<sub>DSON\_HS</sub>) and low-side switch (R<sub>DSON\_LS</sub>); these are equal to:

$$P_{COND} = R_{DSON HS} \cdot I_{OUT}^2 \cdot D + R_{DSON LS} \cdot I_{OUT}^2 \cdot (1 - D)$$

(43)

Where D is the duty cycle of the selected application and is given by:

$$D = \frac{V_{OUT} + (R_{DSON\_LS} + DCRI) \cdot I_{OUT}}{V_{IN} - (R_{DSON_HS} - R_{DSON\_LS}) \cdot I_{OUT}}$$

(44)

In order to obtain a more accurate estimation it is necessary to keep in mind that the amount of resistance of the internal power MOSFET increases with the temperature. For this reason, the value of  $R_{DSONLS}$ , should be increased from the typical of a factor equal to 20%.

Switching losses due to high-side Power MOSFET turn ON and OFF; these can be calculated as:

$$P_{SW} = V_{IN} \cdot I_{OUT} \cdot \frac{(T_{RISE} + T_{FALL})}{2} F_{SW} = V_{IN} \cdot I_{OUT} \cdot T_{SW} \cdot F_{SW}$$

$$\tag{45}$$

Where  $T_{RISE}$  and  $T_{FALL}$  are the overlap times of the voltage across the high-side power switch (VDS) and the current flowing into it during turn ON and turn OFF phases, as shown in Figure 45.  $T_{SW}$  is the equivalent switching time. For this device the typical value for the equivalent switching time is 30 ns.

Quiescent current losses, calculated as:

$$P_Q = V_{IN} \cdot I_{Q,MAX} \tag{46}$$

The quiescent current for constant current operation is equal to 3 [mA]:

The power losses are given by:

$$P_{LOSS} = P_{COND} + P_{SW} + P_O \tag{47}$$

The junction temperature T<sub>J</sub> can be calculated as:

$$T_{I} = T_{A} + R_{thIA} \cdot P_{LOSS} \tag{48}$$

Where  $T_A$  is the ambient temperature.  $R_{thJA}$  is the equivalent thermal resistance junction to ambient of the device; it can be calculated as the parallel of many paths of heat conduction from the junction to the ambient. For this device the path through the exposed pad is the one conducting the largest amount of heat. The  $R_{thJA}$  measured on the demonstration board described in the following section is about 65 °C/W.

DS13554 - Rev 1 page 38/49

It is also possible to estimate the junction temperature directly from the efficiency measurements acquired on a stationary application condition.

Considering that the power losses are given by:

$$P_{LOSS} = P_{IN} - P_{OUT} \tag{49}$$

Neglecting the AC losses of the selected inductor, the power losses related to the L6981 are given by:

$$P_{LOSS L6981} = V_{IN} \cdot I_{IN} - V_{OUT} \cdot I_{OUT} - DCRl \cdot I_{OUT}^{2}$$

$$\tag{50}$$

Consequently, the junction temperature TJ can be calculated as:

$$T_{J} = T_{A} + R_{thJA} \cdot P_{LOSS, L6981} \tag{51}$$

DS13554 - Rev 1 page 39/49

## 12 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

DS13554 - Rev 1 page 40/49

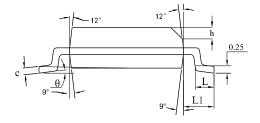

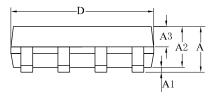

## 12.1 SO 8L package information

Figure 46. SO 8L package outline

SIDE VIEW

SIDE VIEW

TOP VIEW

DS13554 - Rev 1 page 41/49

Table 10. SO 8L mechanical data

| Sym.   | mm   |         |       |

|--------|------|---------|-------|

| Sylli. | Min. | Тур.    | Max.  |

| Α      | -    | -       | 1.75  |

| A1     | 0.10 | -       | 0.225 |

| A2     | 1.30 | 1.40    | 1.50  |

| A3     | 0.60 | 0.65    | 0.70  |

| b      | 0.39 | -       | 0.47  |

| b1     | 0.38 | 0.41    | 0.44  |

| С      | 0.20 | -       | 0.24  |

| c1     | 0.19 | 0.20    | 0.21  |

| D      | 4.80 | 4.90    | 5.00  |

| E      | 5.80 | 6.00    | 6.20  |

| E1     | 3.80 | 3.90    | 4.00  |

| е      |      | 1.27BSC |       |

| L1     |      | 1.05REF |       |

| h      | 0.25 | -       | 0.50  |

| L      | 0.50 | -       | 0.80  |

| Θ      | 0    | -       | 8°    |

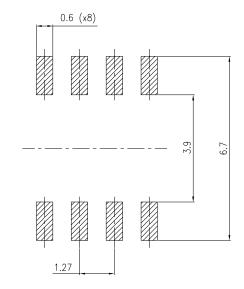

Figure 47. SO 8L recommended footprint

DS13554 - Rev 1 page 42/49

# 13 Ordering information

Table 11. Order codes

| Part numbers | Light-load behavior        | Package | Packaging     |

|--------------|----------------------------|---------|---------------|

| L6981CDR     | LCM (Low Consumption Mode) | SO 8L   | Tape and reel |

| L6981NDR     | LNM (Low Noise Mode)       | SO 8L   | Tape and reel |

DS13554 - Rev 1 page 43/49

## **Revision history**

Table 12. Document revision history

| Date        | Version | Changes        |

|-------------|---------|----------------|

| 15-Jan-2020 | 1       | First release. |

DS13554 - Rev 1 page 44/49

#### **Contents**

| 1 | Diag                     | ıram                        |                                                                         | 2  |

|---|--------------------------|-----------------------------|-------------------------------------------------------------------------|----|

| 2 | Pin                      | configu                     | ration                                                                  | 3  |

| 3 | Турі                     | Typical application circuit |                                                                         |    |

| 4 | Absolute maximum ratings |                             |                                                                         | 5  |

| 5 | Elec                     | Electrical characteristics  |                                                                         |    |

| 6 | Fun                      | ctional                     | descriptiondescription                                                  | 8  |

|   | 6.1                      | Enable                      | <b>;</b>                                                                | 8  |

|   | 6.2                      | Soft-st                     | art                                                                     | 9  |

|   | 6.3                      | Under                       | voltage lockout                                                         | 10 |

|   | 6.4                      | Light-lo                    | oad operation                                                           | 10 |

|   |                          | 6.4.1                       | Low consumption mode (LCM)                                              | 10 |

|   |                          | 6.4.2                       | Low noise mode (LNM)                                                    | 14 |

|   |                          | 6.4.3                       | Efficiency for Low consumption mode and Low noise mode part number      | 15 |

|   |                          | 6.4.4                       | Load regulation for low consumption mode and low noise mode part number | 16 |

|   | 6.5                      | Overvo                      | oltage protection                                                       | 16 |

|   |                          | 6.5.1                       | Low consumption mode part number                                        | 17 |

|   |                          | 6.5.2                       | Low noise mode part number                                              | 18 |

|   | 6.6                      | Overcu                      | urrent protection                                                       | 18 |

|   | 6.7                      | Thermal shutdown            |                                                                         |    |

| 7 | Clos                     | sing the                    | loop                                                                    | 21 |

|   | 7.1                      | GCO(s                       | s) control to output transfer function                                  | 21 |

|   | 7.2                      | Error a                     | amplifier compensation network                                          | 22 |

|   | 7.3                      | Voltage                     | e divider                                                               | 23 |

| 8 | Des                      | ign of th                   | ne power components                                                     | 24 |

|   | 8.1                      | Progra                      | mmable power up threshold                                               | 24 |

|   | 8.2                      | Extern                      | al synchronization (only available for Low Noise Mode)                  | 24 |

|   | 8.3                      | Output                      | voltage adjustment                                                      | 25 |

|   | 8.4                      | Design                      | of the power components                                                 | 26 |

|   |                          | 8.4.1                       | Input capacitor selection                                               | 26 |

|     | 8.4.2             | Inductor selection         | 27 |

|-----|-------------------|----------------------------|----|

|     | 8.4.3             | Output capacitor selection | 27 |

| 9   | Application       | board                      | 29 |

| 10  | Efficiency c      | curves                     | 32 |

| 11  | Thermal dis       | sipation                   | 38 |

| 12  | Package inf       | formation                  | 40 |

|     | <b>12.1</b> SO 8L | package information        | 41 |

| 13  | Ordering in       | formation                  | 43 |

| Rev | ision history     |                            | 44 |

#### **List of tables**

| Table 1.  | Pin description                                                                                      | - 3 |

|-----------|------------------------------------------------------------------------------------------------------|-----|

| Table 2.  | Typical application components                                                                       | 4   |

| Table 3.  | Absolute maximum ratings                                                                             | 5   |

| Table 4.  | ESD performance                                                                                      | 5   |

| Table 5.  | Thermal data                                                                                         | 5   |

| Table 6.  | Electrical characteristics T <sub>J</sub> = 25 °C, V <sub>IN</sub> = 24 V unless otherwise specified | 6   |

| Table 7.  | External synchronization AC coupling suggested operation range                                       | 25  |

| Table 8.  | Input capacitors                                                                                     | 27  |

| Table 9.  | Bill of material                                                                                     | 30  |

| Table 10. | SO 8L mechanical data                                                                                | 42  |

| Table 11. | Order codes                                                                                          | 43  |

| Table 12. | Document revision history                                                                            | 44  |

# **List of figures**

| Figure 1.  | Block diagram                                                                                                  |     |

|------------|----------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Pin connection (top view)                                                                                      | . 3 |

| Figure 3.  | Basic application (adjustable version)                                                                         | . 4 |

| Figure 4.  | Power up/down behavior                                                                                         | . 8 |

| Figure 5.  | Soft-start procedure                                                                                           | . 9 |

| Figure 6.  | Soft-start phase with I <sub>OUT</sub> = 1.25 A                                                                | 10  |

| Figure 7.  | Light-load operation                                                                                           | 11  |

| Figure 8.  | LCM operation with I <sub>SKIP</sub> = 350 mA typ. at zero load. L = 33 $\mu$ H; C <sub>OUT</sub> = 32 $\mu$ F | 11  |

| Figure 9.  | LCM operation over loading condition (part 1-pulse skipping)                                                   | 12  |

| Figure 10. | LCM operation over loading condition (part 2-pulse skipping)                                                   | 12  |

| Figure 11. | LCM operation over loading condition (part 3-pulse skipping)                                                   | 13  |

| Figure 12. | LCM operation over loading condition (part 4-CCM)                                                              | 13  |

| Figure 13. | Low noise mode operation at zero load                                                                          | 14  |

| Figure 14. | Light-load efficiency for low consumption mode and low noise mode - linear scale                               | 15  |

| Figure 15. | Light-load efficiency for low consumption mode and low noise mode - log scale                                  | 15  |

| Figure 16. | Load regulation for LCM and LNM. $V_{IN}$ = 24 V; $V_{OUT}$ = 5 V; $F_{SW}$ = 400 KHz - linear scale           | 16  |

| Figure 17. | Load regulation for low noise mode. $V_{IN}$ = 24 V; $V_{OUT}$ = 5 V; $F_{SW}$ = 400 KHz - log scale           | 16  |

| Figure 18. | OVP event low consumption mode part number                                                                     | 17  |

| Figure 19. | OVP event low noise mode part number                                                                           | 18  |

| Figure 20. | Overcurrent protection behavior                                                                                | 19  |

| Figure 21. | Soft-start procedure with VOUT shorted to GND                                                                  |     |

| Figure 22. | Over current procedure with persistent short circuit between V <sub>OUT</sub> and GND                          | 20  |

| Figure 23. | Block diagram of the loop                                                                                      | 21  |

| Figure 24. | Trans-conductance embedded error amplifier                                                                     | 22  |

| Figure 25. | Leading network example                                                                                        | 23  |

| Figure 26. | Leading network example                                                                                        | 24  |

| Figure 27. | External synchronization. Direct connection                                                                    | 24  |

| Figure 28. | External synchronization. AC coupling                                                                          |     |

| Figure 29. | Application circuit                                                                                            |     |

| Figure 30. | Evaluation board schematic                                                                                     |     |

| Figure 31. | Top layer                                                                                                      |     |

| Figure 32. | Bottom layer                                                                                                   |     |

| Figure 33. | Efficiency $V_{IN}$ = 24 V; $V_{OUT}$ = 5 V; $F_{SW}$ = 0.4 MHz                                                |     |

| Figure 34. | Efficiency $V_{IN}$ = 24 V; $V_{OUT}$ = 5 V; $F_{SW}$ = 0.4 MHz (log scale)                                    |     |

| Figure 35. | Power losses V <sub>IN</sub> = 24 V; V <sub>OUT</sub> = 5 V; F <sub>SW</sub> = 0.4 MHz                         | 33  |

| Figure 36. | Efficiency $V_{IN}$ = 12 V; $V_{OUT}$ = 5 V; $F_{SW}$ = 0.4 MHz                                                | 33  |

| Figure 37. | Efficiency V <sub>IN</sub> = 12 V; V <sub>OUT</sub> = 5 V; F <sub>SW</sub> = 0.4 MHz (log scale)               | 34  |

| Figure 38. | Power losses V <sub>IN</sub> = 12 V; V <sub>OUT</sub> = 5 V; F <sub>SW</sub> = 0.4 MHz                         | 34  |

| Figure 39. | Efficiency V <sub>IN</sub> = 24 V; V <sub>OUT</sub> = 3.3 V; FSW = 0.4 MHz                                     | 35  |

| Figure 40. | Efficiency V <sub>IN</sub> = 24 V; V <sub>OUT</sub> = 3.3 V; F <sub>SW</sub> = 0.4 MHz (log scale)             | 35  |

| Figure 41. | Power losses V <sub>IN</sub> = 24 V; V <sub>OUT</sub> = 3.3 V; F <sub>SW</sub> = 0.4 MHz                       | 36  |

| Figure 42. | Efficiency V <sub>IN</sub> = 12 V; V <sub>OUT</sub> = 3.3 V; F <sub>SW</sub> = 0.4 MHz                         | 36  |

| Figure 43. | Efficiency V <sub>IN</sub> = 12 V; V <sub>OUT</sub> = 3.3 V; F <sub>SW</sub> = 0.4 MHz (log scale)             |     |

| Figure 44. | Power losses V <sub>IN</sub> = 12 V; V <sub>OUT</sub> = 3.3 V; F <sub>SW</sub> = 0.4 MHz                       |     |

| Figure 45. | Switching losses                                                                                               |     |

| Figure 46. | SO 8L package outline                                                                                          |     |

| Figure 47. | SO 8L recommended footprint                                                                                    |     |

|            |                                                                                                                |     |

DS13554 - Rev 1 page 48/49

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

DS13554 - Rev 1 page 49/49