TOSHIBA CMOS Linear Integrated Circuit Silicon Monolithic

# **TCKE805 Series**

# 18 V, 5A eFuse IC with Adjustable Over Current Protection and Reverse Blocking FET Control

The TCKE805 series are 18 V high input voltage Single Inputs—Single Output eFuse IC. It can be used as a reusable fuse, and includes protection features like adjustable over current limit by an external resistor, short circuit protection, over voltage clamp, adjustable slew rete control by an external capacitance, under voltage protection, thermal shutdown and reverse current blocking by external MOSFET control circuit.

Switch ON resistance is only 28 m $\Omega$ , high output current is up to 5.0A, and wide input voltage operation characteristics makes this product ideal for power management applications such as in the power supply circuit of hard disk drive and battery charging applications.

This device is available in 0.4mm pitch small package WSON10B (3.0 mm x 3.0 mm, t: 0.7 mm (typ)). Thus this devices is ideal for various applications such as portable electronics that require high-density boards.

Weight: 19.3mg (typ.)

#### **Feature**

- High input voltage: V<sub>IN max</sub> = 18.0 V

- High output current: I<sub>OUT</sub> (DC) = 5.0 A

- Low ON resistance :  $R_{ON} = 28 \text{ m}\Omega$  (typ.)

- Adjustable overcurrent limit : up to 5.0 A

- · Fixed over voltage clamp

- 5V power rail: 6.04 V (typ.)

- · Programmable slew rate control by external capacitance for Inrush current reduction

- Programmable under voltage lockout by external resistor

- · Reverse current blocking support by built in MOSFET Driver

- · Adjustable under voltage lockout(UVLO) by external resistor

- Thermal shutdown

- Auto-discharge

- · Small package:

WSON10B (3.0 mm x 3.0 mm, t: 0.7 mm (typ))

#### **Notice**

This device is sensitive to electrostatic discharge.

Please ensure equipment and tools are adequately earthed when handling.

Start of commercial production 2019-11

#### Absolute Maximum Ratings (Ta = 25°C)

| Characteristics         | Symbol                           | Rating                                                   | Unit |

|-------------------------|----------------------------------|----------------------------------------------------------|------|

| Input voltage           | VIN                              | -0.3 to 18.0                                             | V    |

| ILIM voltage            | VILIM                            | -0.3 to 6.0                                              | V    |

| dV/dT voltage           | V <sub>d</sub> V/ <sub>d</sub> T | -0.3 to 6.0                                              | V    |

| Control voltage         | VEN/UVLO                         | -0.3 to 18.0                                             | V    |

| Output voltage          | Vout                             | -0.3 to V <sub>IN</sub> + 0.3 or 18.0 V which is smaller | V    |

| External MOSFET voltage | VEFET                            | -0.3 to 30.0                                             | V    |

| Power dissipation       | PD                               | 2.4 (Note 1)                                             | W    |

| Junction temperature    | Tj                               | 150                                                      | °C   |

| Storage temperature     | T <sub>stg</sub>                 | -55 to 150                                               | °C   |

Note: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings. Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook ("Handling Precautions"/"Derating Concept and Methods") and individual reliability data (i.e. reliability test report and estimated failure rate, etc).

Note1: Rating at mounting on a board: FR4 board. (76.2mm \* 114.3mm \* 1.6mm, 4 layer )

**Operating Ranges**

| beruting ranges                      |                    |                                    |      |    |  |

|--------------------------------------|--------------------|------------------------------------|------|----|--|

| Characteristics                      | Symbol             | Ran                                | Unit |    |  |

| Input voltage                        | VIN                | 4.4 to                             | V    |    |  |

| Output current                       | lout               | Continuous output current 0 to 5.0 |      | А  |  |

| I <sub>LIM</sub> External resistance | RILIM              | 20 to 300                          |      | kΩ |  |

| Control voltage                      | VEN/UVLO           | 0 to 18                            |      | V  |  |

| External MOSFET voltage              | VEFET              | 0 to V <sub>IN</sub> + 4.9         |      | V  |  |

| Operating Ambient temperature range  | Ta_opr             | -40 to 85                          |      | °C |  |

| External capacitance                 | C <sub>dV/dT</sub> | 1 (typ), 100 (max)                 |      | nF |  |

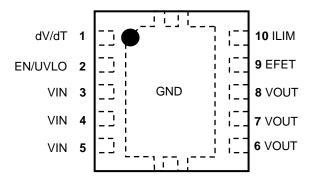

# **Pin Assignment (Top view)**

WSON10B

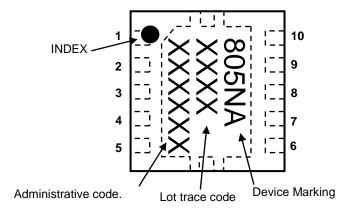

# **Top Marking (Top view)**

Example: TCKE805NA

| Product list |              |             |            |         |                                            |

|--------------|--------------|-------------|------------|---------|--------------------------------------------|

| Part number  | Over voltage | CE          | Fault      | Тор     | Package                                    |

|              | Clamp        | function    | Response   | Marking |                                            |

| TCKE805NA    | 6.04V (typ)  | Active High | Auto-retry | 805NA   | WSON10B (3.0 mm x 3.0 mm, t: 0.7 mm (typ)) |

| TCKE805NL    | 6.04V (typ)  | Active High | Latched    | 805NL   | WSON10B (3.0 mm x 3.0 mm, t: 0.7 mm (typ)) |

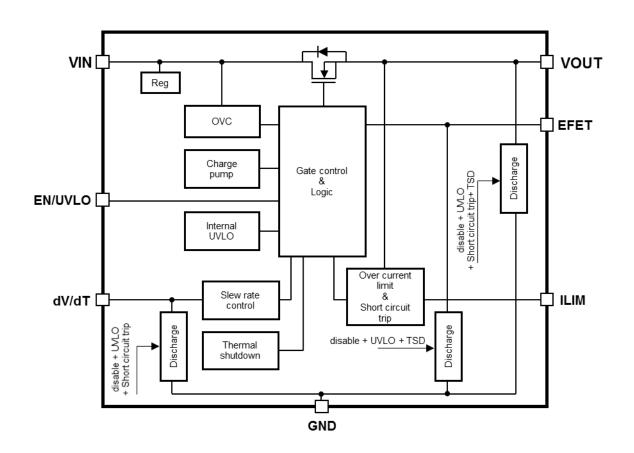

# **Block Diagram**

# **PIN Description**

| PIN Name | Description                                                                                |

|----------|--------------------------------------------------------------------------------------------|

| EN/UVLO  | This pin has two functions. One function turns on the output voltage of the internal       |

|          | MOSFET and EFET terminal as an enable signal. Another function can be used as a            |

|          | UVLO trip point with external resistors.                                                   |

| ILIM     | Current limit set input. A resistor between ILIM terminal and GND set the current limit.   |

| dV/dT    | Rise time set input. A capacitor between dV/dT terminal and GND set the slew rate of       |

| av/a1    | VOUT when the device turns on.                                                             |

| EFET     | Connect this pin to the gate of a blocking Nch MOSFET. This pin can be left floating if it |

| EFEI     | is not used                                                                                |

| VIN      | Supply Input. Input to the power switch and the supply voltage for the device.             |

| GND      | Ground.                                                                                    |

| VOUT     | Output. Output of the power switch.                                                        |

# **Operation Logic Table**

|        | EN/UVLO "Low" | EN/UVLO " High" |

|--------|---------------|-----------------|

| Output | OFF           | ON              |

# TCKE805 series DC Characteristics (Unless otherwise specified, Ta = -40 to 85°C, VIN = 5V, RILIM = $20k\Omega$ )

| Charactariation                                    | Cumbal                           | Tool Oos dilion                                                                         | Ta = 25°C |                           |      | Ta = -40 to 85°C |         | 1.1-21 |

|----------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------|-----------|---------------------------|------|------------------|---------|--------|

| Characteristics                                    | Symbol                           | Test Condition                                                                          | Min.      | Тур.                      | Max. | Min.             | Max.    | Uni    |

| Basic operation                                    |                                  |                                                                                         |           |                           |      |                  |         |        |

| VIN under voltage lockout (UVLO) threshold, rising | VIN_UVLO                         |                                                                                         | _         | 4.15                      | _    | 4.00             | 4.40    | V      |

| VIN under voltage lockout (UVLO) hysteresis        | VIN_UVhyst                       |                                                                                         | _         | 5                         | _    | _                | _       | %      |

| EN/UVLO threshold voltage, rising                  | V <sub>ENR</sub>                 | _                                                                                       |           | 1.1                       |      | 1.0              | 1.2     | V      |

| EN/UVLO threshold voltage, falling                 | V <sub>ENF</sub>                 | _                                                                                       |           | 0.96                      | _    | 0.89             | 1.01    | V      |

| On resistance                                      | Ron                              | I <sub>OUT</sub> = 1.5 A                                                                | _         | 28                        | _    | _                | 38      | mΩ     |

| Quiescent current (ON state)                       | IQ                               | $V_{EN} = 3 \text{ V}, \text{ R}_{ILIM} = 120 \text{ k}\Omega,$ $I_{OUT} = 0 \text{ A}$ | _         | 0.46                      | _    | _                | 0.61    | m/     |

| Quiescent current (OFF state)                      | IQ(OFF)                          | EN = 0V                                                                                 | _         | 33                        | _    | _                | 48      | μΑ     |

| dV/dT control                                      |                                  |                                                                                         |           |                           |      |                  |         |        |

| Capacitor Voltage                                  | V <sub>d</sub> V/ <sub>d</sub> T | _                                                                                       | _         | 3                         | _    | _                | _       | V      |

| Charging Current                                   | l <sub>dV/dT</sub>               | V <sub>dV/dT</sub> =0V                                                                  | _         | 250                       | _    | _                | _       | nA     |

| Discharge resistance                               | R <sub>dV/dT</sub>               | VEN = 0 V, IdV/dT =10 mA                                                                | _         | 5                         | _    | 3                | 9       | Ω      |

| dV/dT to OUT gain                                  | GAIN <sub>dV/dT</sub>            | (Note2) V <sub>dV/dT</sub> = 0.3 V                                                      | _         | 10.5                      | _    | _                | _       | _      |

| External FET Gate driver                           |                                  |                                                                                         |           |                           |      | •                |         |        |

| Charging Current                                   | I <sub>EFET</sub>                | VEFET = 5 V (Note2)                                                                     | _         | 2                         | _    | _                | _       | μА     |

| Output voltage                                     | VEFET                            | (Note2)                                                                                 | _         | VIN+4.9                   | _    | VIN+4.4          | VIN+5.3 | V      |

| Discharge resistance                               | REFET                            | V <sub>EN</sub> = 0 V, I <sub>EFET</sub> = 20 mA                                        | _         | 24                        | _    | 12               | 40      | Ω      |

| Over-voltage Protection                            |                                  |                                                                                         |           |                           |      | •                |         | •      |

| Over voltage clamp (OVC)                           | Vovc                             | V <sub>IN</sub> = 7 V, I <sub>OUT</sub> = 1 A                                           | _         | 6.04                      | _    | 5.62             | 6.45    | ٧      |

| Over-current Protection                            |                                  |                                                                                         |           |                           |      |                  |         |        |

|                                                    |                                  | $R_{ILIM} = 20 \text{ k}\Omega, V_{IN} - V_{OUT} = 1 \text{ V}$                         | _         | 5.15                      | _    | 4.44             | 5.87    |        |

|                                                    | ILIM<br>(IOUT_CL)                | RILIM = 24 k $\Omega$ , VIN - VOUT = 1 V                                                | _         | 4.38                      | _    | 3.88             | 4.88    | - A    |

|                                                    |                                  | $R_{ILIM} = 35.1 \text{ k}\Omega, V_{IN} - V_{OUT} = 1 \text{ V}$                       | _         | 3.06                      | _    | 2.70             | 3.41    |        |

|                                                    |                                  | $R_{ILIM} = 62 k\Omega$ , $V_{IN} - V_{OUT} = 1 V$                                      | _         | 1.78                      | _    | 1.52             | 2.04    |        |

| Over current limit (Note3)                         |                                  | RILIM = 120 k $\Omega$ , VIN - VOUT = 1 V                                               |           | 0.96                      | _    | 0.76             | 1.16    |        |

|                                                    |                                  | $R_{ILIM} = 250 \text{ k}\Omega, V_{IN} - V_{OUT} = 1 \text{ V}$                        |           | 0.50                      | _    | 0.35             | 0.65    |        |

|                                                    |                                  | R <sub>ILIM</sub> = 0 Ω, V <sub>IN</sub> - V <sub>OUT</sub> = 1 V                       | _         | 0.64                      | _    | _                | _       |        |

|                                                    |                                  | RILIM = OPEN, VIN - VOUT = 1 V                                                          |           | 0.64                      | _    | _                |         |        |

| Short-circuit current limit                        | I <sub>SCL</sub>                 | (Note2),(Note4)                                                                         | _         | 0.15                      | _    | 0.05             | 0.50    | Α      |

| Fast trip comparator level                         | IFASTTRIP<br>(ISHORT_TRIP)       | _                                                                                       | _         | I <sub>LIM</sub> ×<br>1.6 | _    | _                | _       | Α      |

| ILIM short resistor detect Threshold               | RSHORTLIM                        | _                                                                                       | _         | 11                        | _    | _                | _       | kΩ     |

| Thermal Protection                                 |                                  | •                                                                                       |           | •                         |      |                  |         |        |

| Thermal shut down Threshold                        | T <sub>SD</sub>                  | Тј                                                                                      | _         | 160                       | _    | _                | _       | °C     |

| Thermal shut down Hysteresis                       | T <sub>SDH</sub>                 | Tj                                                                                      |           | 20                        | _    | _                | _       | °C     |

Note2: This parameter is warranted by design.

Note3: Pulsed testing techniques used during this test maintain junction temperature approximately equal to ambient temperature.

Note4: Hard short less than 10 m $\Omega$ .

# TCKE805 AC Characteristics (Unless otherwise specified, Ta = -40 to 85°C, VIN = 5V, RILIM = 20k $\Omega$ , RLOAD=5 $\Omega$ , CIN = COUT = 1 $\mu$ F )

| Characteristics            | Symbol      | Test Condition                                                                                                  |   | Тур. | Max. | Unit |

|----------------------------|-------------|-----------------------------------------------------------------------------------------------------------------|---|------|------|------|

| V <sub>OUT</sub> on time   | ton         | VEN↑ to I <sub>IN</sub> = 100 mA, 1 A resistive load at V <sub>OUT</sub> ,<br>C <sub>dV/dT</sub> = OPEN (Note5) |   | 330  | _    | μS   |

| Vout off time              | tOFF        | VEN↓ to VEFET↓, CEFET = OPEN (Note5)                                                                            | _ | 0.96 | _    | μS   |

| Output ramp time           | tdV/dT      | V <sub>EN</sub> ↑ to V <sub>OUT</sub> become V <sub>IN</sub> * 90%, C <sub>dV/dT</sub> = OPEN (Note6)           |   | 400  | 700  | μS   |

|                            |             | V <sub>EN↑</sub> to V <sub>OUT</sub> become V <sub>IN</sub> * 90%, C <sub>dV/dT</sub> = 1 nF (Note5)            | _ | 2.3  | _    | ms   |

| Fast trip comparator delay | tFastOffDly | IOUT > IFASTTRIP to IOUT = 0 (Switch off) (Note5)                                                               |   | 150  | _    | ns   |

| EFET on time               | tefet-on    | VEN↑ to VEFET = VIN, CEFET = 1 nF(Note5)                                                                        |   | 2.6  |      | ms   |

|                            |             | V <sub>EN↑</sub> to V <sub>EFET</sub> = V <sub>IN</sub> , C <sub>EFET</sub> = 10 nF(Note5)                      | _ | 25   | _    | ms   |

| FFFT ""                    | tefet-off   | V <sub>EN</sub> ↓ to V <sub>EFET</sub> = 1 V, C <sub>EFET</sub> = 1 nF(Note5)                                   |   | 1.2  |      | μS   |

| EFET off time              |             | V <sub>EN</sub> ↓ to V <sub>EFET</sub> = 1 V, C <sub>EFET</sub> = 10 nF(Note5)                                  | _ | 2.9  | _    | μS   |

Note5: This parameter is reference only. Note6: This parameter is warranted by design.

#### **Application Note**

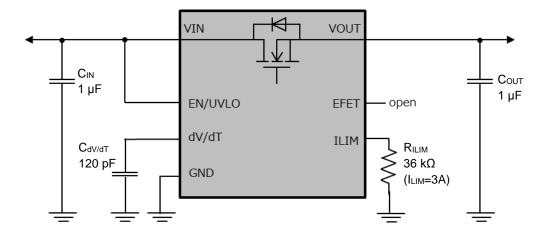

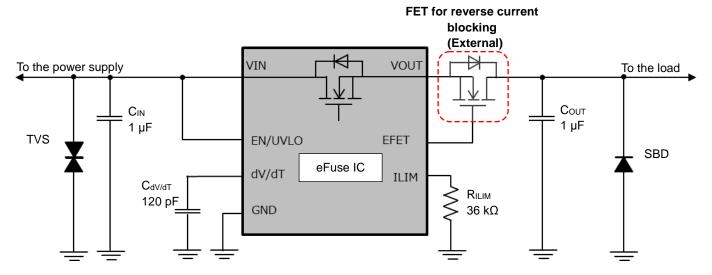

#### 1. Application circuit example

#### 1) Peripheral circuits

Connect the power supply to the input terminal  $V_{IN}$ . During normal operation, almost the same voltage as the  $V_{IN}$  voltage is output from the output terminal  $V_{OUT}$  through the internal MOSFET.

If the current suddenly decreases, for example, when short-circuiting or overcurrent is protected, high-spike voltages may be generated due to back electromotive force of inductance components such as wirings connected to the input/output terminals of the eFuse IC, causing damage to the eFuse IC and resulting damage. In this case, a positive spike voltage is generated on the input side and a negative spike voltage is generated on the output side.

When designing boards, design patterns so that the length of the wires on the input-side and output-side of the eFuse IC is as short as possible. Also, the GND wiring area should be as wide as possible to reduce the impedance.  $C_{IN}$  functions to suppress the peak value against the positive spike voltage generated by the inputs. The peak value  $V_{SPIKE}$  of the spike voltage and the capacitance value of the  $C_{IN}$  have the following relationships. It can be understood that the spike voltage can be reduced by increasing the  $C_{IN}$ .

$$V_{SPIKE}(V) = V_{IN} + I_{OUT} \times \sqrt{\frac{L_{IN}}{C_{IN}}}$$

L IN: effective inductance component of the input terminal (H), I OUT: output current (A)

V SPIKE: peak value of spiked voltage generated (V), V IN: power supply voltage during normal operation (V)

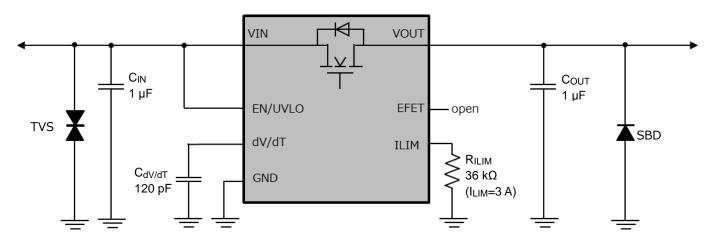

Toshiba eFuse IC recommends 1  $\mu$ F for  $C_{IN}$  and  $C_{OUT}$ , and in most cases this volume is effective enough. Be sure to measure it on the actual PCB board. In order to prevent damage due to spike voltage, it is also recommended to connect a TVS diode (ESD protection diode) to the input terminal and a SBD (Schottky barrier diode) to the output terminal.

TVS diodes are also effective in preventing surge damage caused by external noises input from power supplies and GND wires. In addition to protecting the eFuse IC, TVS diodes are also effective in preventing damage to ICs and devices on the load side. For eFuse IC use, connect between the input terminal and GND. For negative spike voltage generated on the output side, an SBD can be connected to prevent the output potential from dropping more than GND. This protects not only the eFuse IC but also the ICs and devices connected as loads. Connect the SBD with the GND as the anode between the output terminal of the eFuse IC and the GND.

As noted above, TVS diodes and SBDs are recommended for eFuse IC because they can provide more robust protective features. The diagram below shows the peripheral circuit diagram when a TVS diode and an SBD are added.

Our eFuse IC recommends DF2S23P2CTC as the TVS diode and CUHS20F30 as the SBD diode.

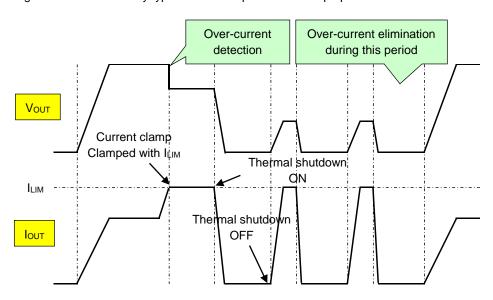

#### 2) Operation of the thermal shutdown function

The overcurrent protection function prevents damage to the IC and load by suppressing power consumption in the event of an error. If the output current exceeds the limit current (I LIM) due to a load error or short circuit, the output voltage and output current also decrease, thereby limiting the power consumed by the ICs and the load.

In addition to the short-circuit protection function, which will be described later, it is double-protected against overcurrent, which greatly contributes to the prevention of ignition and smoke.

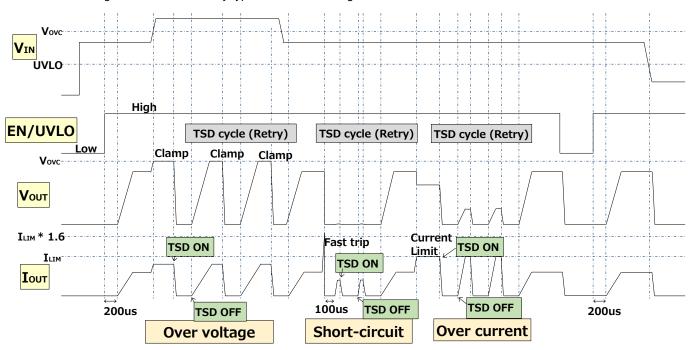

The timing chart of the auto-retry type overcurrent protection clamp operation is shown below.

Timing chart of overcurrent protection operation (auto-retry type)

When the output current reaches ILIM and overcurrent is detected, the output current is clamped so that no more current than ILIM flows. At this time, the output voltage drops slightly according to the relationship between the output voltage and the current, which will be described later. If the overcurrent is not resolved at this stage, this condition is maintained and the IC temperature continues to rise. Soon the IC reaches the operating temperature of the thermal shutdown function, the MOSFET is switched off, and the eFuse IC stops operating.

Next, the timing chart of the overcurrent protection clamp operation of the latch type is shown in the figure below. This condition is maintained until the latch type is restarted by the control signals of the EN/UVLO terminal. However, the auto-retry type repeats the restoration attempt by stopping the operation  $\rightarrow$  lowering the temperature  $\rightarrow$  releasing the thermal shutdown  $\rightarrow$  clamping the current  $\rightarrow$  protecting the overheat  $\rightarrow$  raising the temperature  $\rightarrow$  protecting the overheat  $\rightarrow$  Stopping the operation until the overcurrent is eliminated.

Timing chart of overcurrent protection operation (latch type)

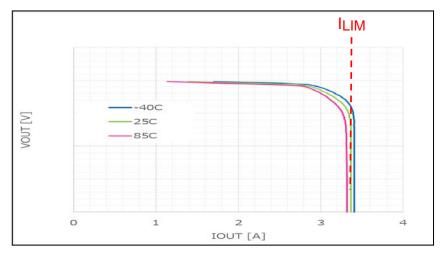

#### 3) Setting the overcurrent protection function

The following figure shows the relationship between output voltage and current during overcurrent protection clamp operation.

Output Voltage-Current Characteristics during Overcurrent Protection Clamp Operation

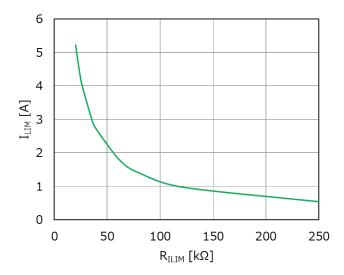

Toshiba eFuse IC has a variable current limit. By selecting the external resistor  $R_{\text{ILIM}}$  of the  $I_{\text{LIM}}$  terminal appropriately, the current limit can be set to the optimum value for each application. The  $I_{\text{LIM}}$  calculations are the same as those for the TCKE8 series, and are as shown below. However, the deviation between the theoretical value and the measured value is large when the current is 1A or higher. Be sure to check the resistance value with the actual machine when selecting the resistance value.

$$I_{LIM}(A) = 0.13 + 101.8/R_{ILIM}(k\Omega)$$

R<sub>ILIM</sub>: I<sub>LIM</sub> terminal external resistor (kΩ)

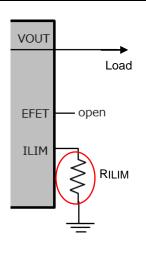

The following is a diagram of the peripheral circuitry of the  $I_{LIM}$  terminal and the relation between  $R_{ILIM}$  and  $I_{LIM}$ .

**ILIM Terminal External Circuits**

RILIM-ILIM Characteristics

For reference table below shows the resistivity of the RILIM and the current ILIM.

|                        | •                           |              |

|------------------------|-----------------------------|--------------|

| R <sub>ILIM</sub> (kΩ) | I <sub>LIM</sub> (A) (typ.) | Conditions   |

| 20                     | 5.15                        |              |

| 24                     | 4.38                        |              |

| 36                     | 3.00                        |              |

| 62                     | 1.78                        | VIN-VOUT=1 V |

| 120                    | 0.96                        | VIN-VOUT=I V |

| 250                    | 0.5                         |              |

| 0                      | 0.64                        |              |

| OPEN                   | 0.64                        |              |

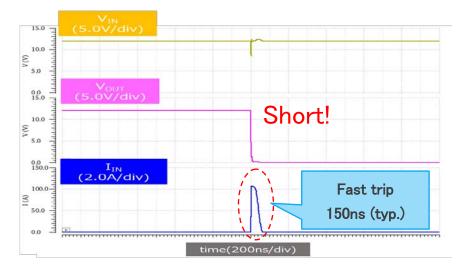

#### 4) Short Circuit protection

The short-circuit protection function prevents excessive current from flowing by stopping operation when the power supply line or load is short-circuited due to some kind of abnormality. If the output current is 1.6 times the current limit (I<sub>LIM</sub>) for a very short period of time, the output is judged to be short-circuited and this function operates.

Toshiba eFuse IC employs an ultra-high-speed short-circuit protecting circuit (Fast trip function). Simulation results are shown to suppress the current to near zero at 150 ns (typ.) from the occurrence of the short-circuit.

The following table shows the operating waveforms of the simulated Fast trip function.

Output voltages and output current waveforms during fast trip operation

The short-circuit protection circuit performs the return operation 100 µs after Fast trip. If the short-circuit continues, the protection operation starts again. The latch type does not attempt to recover thereafter, but continues to be

protected until it is restarted by the control signal. The auto-retry type attempts to recover until the short-circuit condition is resolved by using the thermal shutdown cycle.

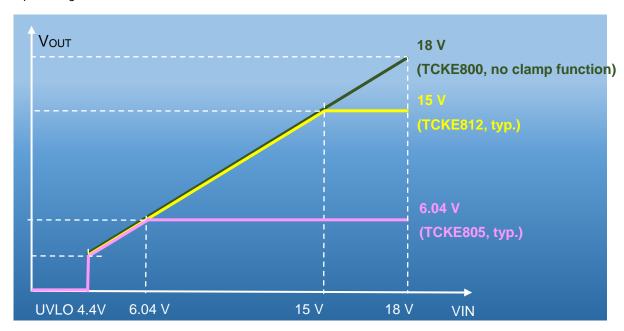

#### 5) Overvoltage protection function

The overvoltage clamp function clamps the output voltage with a limited voltage and prevents overvoltage from being applied to the load without outputting any more voltage. This function is available on the TCKE805/812 series and is not included in the TCKE800 series. The limit voltages are set to 6.04 V (standard) for the TCKE805 series and 15 V (standard) for the TCKE812 series. The diagram below shows the relation between the input voltage and the output voltage of TCKE800/805/812 series.

Overvoltage Characteristics of TCKE800/805/812

Similar to the overcurrent protection and short-circuit protection, the auto-retry type will attempt to recover from the overvoltage, but the latch type will retain this state until it is restarted.

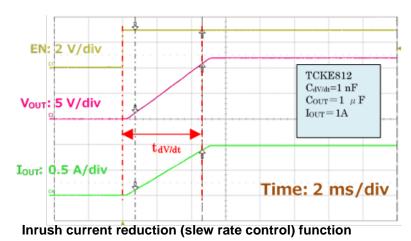

#### 6) Inrush current reduction

When the output is turned on, an inrush current flows to charge the capacitor connected to the load side. If this current is too large, the overcurrent protection circuit may malfunction, making it impossible to start up, or the output voltage may overshoot.

To prevent this, this function controls the slew rate when the output voltage rises by limiting the inrush current.

The following figure shows the rise of the output voltage (V OUT) and the inrush current when the inrush current is limited by this function. As shown below, the output current at the start-up is gradually increasing.

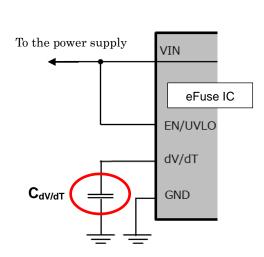

#### 7) Setting of slew rate control for inrush current reduction

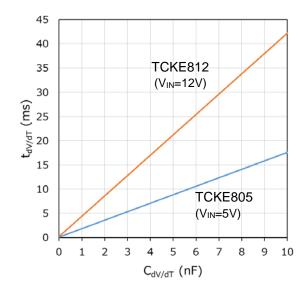

To shiba eFuse IC has a variable inrush current function. The external capacitor at the dV/dT terminal can be used to appropriately set the rise time ( $t_{dV/dT}$ ) of the output voltage. The formula for the rise time is as follows:

$$tdv/dt$$

(s) =  $0.36 \times 10^{6} \times VIN \times (CdVdT+50 \times 10^{-12}) + 3.0 \times 10^{-4}$

V<sub>IN</sub>: input voltage (V), C<sub>dV/dT</sub>: external capacitance of dV/dT terminal (F)

The following chart shows the peripheral circuit diagram of the dV/dT terminal and graphs showing the relation between CdV/dT and tdV/dT.

C<sub>dV/dT</sub>-t<sub>dV/dT</sub> Characteristics of External Circuits around dV and dT Terminals

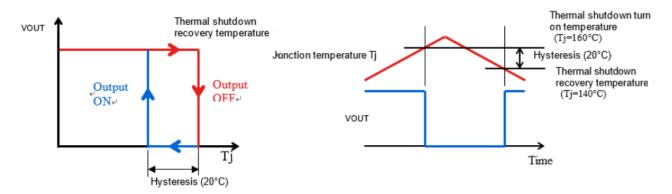

#### 8) Thermal shutdown function

Thermal shutdown (overheat protection) is a function to shut off and protect the output by setting the IC to standby when a large current continues to flow to the output and the junction temperature of the eFuse IC exceeds the set temperature.

The following figure shows the operation image of the thermal shutdown function. When the thermal shutdown is activated, no current flows through the IC, and the junction temperature begins to drop. Hysteresis is given to the operating temperature and the recovery temperature of the thermal shutdown. The IC will not recover until the temperature drops after a certain period of time.

Operation of thermal shutdown function

#### 9) Reverse current blocking

As an option, Toshiba eFuse IC can prevent reverse current flow by attaching an N-channel MOSFET to the EFET terminal. The reverse current blocking function prevents reverse current from the output side to the input side when the operation of the eFuse IC is stopped, for example, by turning off the power supply of the VIN or controlling the input side by the EN/UVLO terminal.

The circuit for using the reverse current blocking function is shown in the figure below.

Fig. 3.12 Examples of eFuse IC Peripheral Circuits with Reverse current blocking Function

Our SSM6K513NU is recommended as an external FET to prevent backflow. SSM6K513NU main characteristics are as follows:

- Drain-source voltage: V<sub>DSS</sub> = 30 V

- Gate-Source Voltage: V<sub>GSS</sub> = 20 V

- Drain current: I<sub>D</sub> = 15 A

- Drain-source on-resistance: R<sub>DS (ON)</sub> =8 mΩ @VGS=4.5 V

When using other products, select a product with as low of on-resistance as possible, with sufficient  $V_{DSS}$  and  $I_{D}$  margins for the power supply voltage and the load current that is expected to be used.

The EFET terminal outputs the internally boosted voltage VIN+4.9V (typ.). If this function is not used, open the terminal.

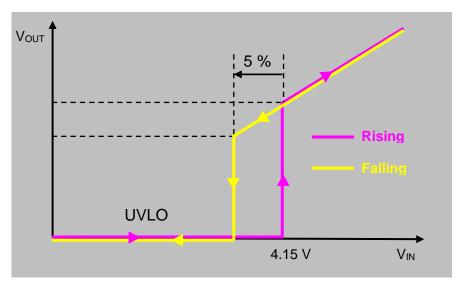

#### 10) Under voltage lockout function (UVLO)

This function stops the operation of the eFuse IC when the input voltage is low and prevents malfunction of the load. The TCKE8 series will not operate unless the input voltage exceeds 4.15 V (typ.). This voltage has hysteresis at the rising and falling edges. At the falling edge, the voltage stops at 5% (typ.) lower than 4.15 V at the rising edge (about 3.95 V).

The following figure shows the operation of this function.

#### 11) EN/UVLO terminal function

The TCKE8 series is equipped with EN/UVLO terminal, and this terminal can be used to control the operation of the whole eFuse IC. It is also possible to set the operating voltage of the under voltage lockout function to the optimum value by externally attaching a resistor.

The following are examples of uses for this terminal.

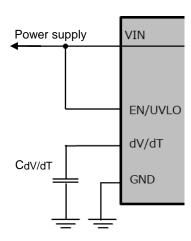

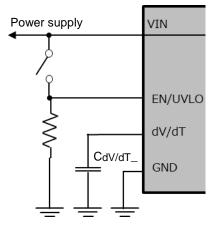

(1) When the operation voltage of the under voltage lockout function is not changed or the operation control is not performed.

Connections of EN/UVLO terminals (Direct V<sub>IN</sub> connection)

Connect the EN/UVLO terminal directly to the  $V_{IN}$  terminal. This eliminates the need for pull-up resistors in the TCKE8 series. The EN/UVLO terminal is designed to be breakdown-voltage 18 V, and the  $V_{IN}$  terminal and the EN/UVLO terminal can be directly connected. This helps reduce the number of parts.

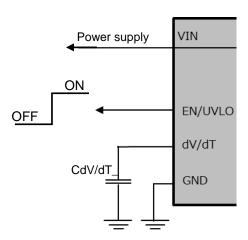

(2) When the operation voltage of the under voltage lockout function is not changed and the operation control is performed from the outside.

Connecting Examples of EN/UVLO Terminals (External Control)

Connect external control signals directly into the EN/UVLO terminal. Since the on/off threshold voltages of the EN/UVLO terminals are hysteretic, set the "H" level of the control signal to be 1.1 V (typ.) or higher and the "L" level of the control signal to be 0.96 V (typ.)or lower.

If the EN/UVLO terminal is open (indefinite), the eFuse IC operation may become abnormal. Be careful not to open this terminal even when it is at the "L" level.

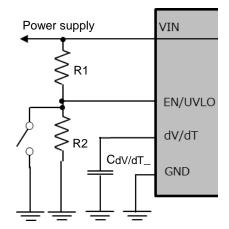

(3) When the operation voltage of the under voltage lockout function is not changed and the operation is controlled by the short-circuit switch with the  $V_{IN}$  terminal.

Connection examples of EN/UVLO terminals (connected by V<sub>IN</sub> and switches)

Switches can be directly connected to the  $V_{\text{IN}}$  so that the operation can be controlled. A pull-down resistor is required to prevent the EN/UVLO terminal from being opened when the SW1 is opened. The value of the pull-down resistor may be any value that does not cause the EN/UVLO terminal to become indefinite. However, when the SW1 is conducting, consider the current flowing through R1, and check the value with the actual device to determine the value of the pull-down resistor.

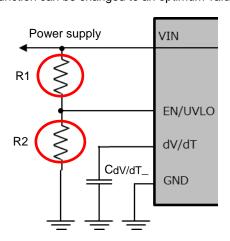

(4) To change the operating voltage of the under voltage lockout function

By adding an external resistor to the EN/UVLO terminal, the operating voltage of the under voltage lockout function can be changed to an optimum value. An example of the circuit is shown in the figure below.

a) In case of no operation control

b) in case of operation control

Connections of EN/UVLO terminals (V<sub>IN</sub> resistive division)

**a)** is an example of the circuit when the operation control is not performed by the EN/UVLO terminal, and **b)** is an example of the circuit when the operation control is performed.

As shown in the drawing, operation is stopped when the input voltage drops by controlling the operation of the EN/UVLO terminal with the voltage obtained by dividing the input voltage by an external resistor. The operating voltage of the under voltage lockout function can be set to the optimum value by properly selecting the external resistance. However, the voltage cannot be set to 4.15 V or less.

The equation for setting  $V_{IN}\_UVLO_{(fall)}$  by controlling the external resistors R1 and R2 of the EN/UVLO terminal is as follows.

$$V_{IN}-UVLO_{(fall)}(V) = \frac{R2}{R1 + R2} \times V_{ENF}(V)$$

V ENF: EN threshold (falling) 0.96 V (typ.)

As described above, the control voltage of the EN/UVLO terminal is hysteretic, and therefore the voltage to be

activated at the time of rising changes. The start-up voltage V<sub>IN</sub>\_UVLO<sub>(rise)</sub> is calculated by the following equation.

$$V_{IN\_}UVLO_{(fall)}(V) = \frac{R2}{R1 + R2} \times V_{ENF}(V)$$

V ENR: EN Threshold Voltage (rising) 1.1 V (typ.)

As shown in **b)** above, the switch can be connected in parallel with R2 to control the operation. In this case, contrary to the case of (3), the eFuse IC stops operating at the time of SW1 conduction. At this time, R1 is the current limiting resistor. Be careful when selecting the resistors for R1 and R2.

#### 12) Precautions regarding protection functions

Toshiba eFuse IC has various protection functions. Be aware that not every function will cause the eFuse IC to cease functioning. When using these products, please read through and understand the concepts described and follow absolute maximum ratings from the information above or from our 'Semiconductor Reliability Handbook'. Please operate these products below absolute maximum ratings in all instances. Furthermore, Toshiba highly recommends inserting failsafe systems into the design.

#### 13) Timing chart

The timing chart of the auto-retry type is shown in the figure below.

Timing chart (auto-retry type)

The timing chart of the latch type is shown in the figure below.

Timing chart (latch type)

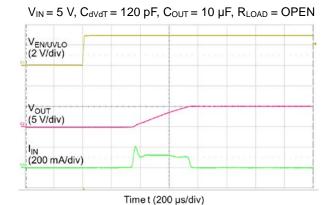

#### Representative Typical Characteristics

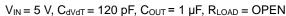

#### ton Response

$V_{IN}$  = 5 V,  $C_{dVdT}$  = 120 pF,  $C_{OUT}$  = 1  $\mu$ F,  $R_{LOAD}$  = 3.3  $k\Omega$

Time t (200 µs/div)

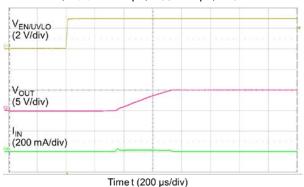

#### toff Response

$$V_{IN}$$

= 5 V,  $C_{dVdT}$  = 120 pF,  $C_{OUT}$  = 1  $\mu$ F,  $R_{LOAD}$  = 3.3  $k\Omega$

Time t (200 µs/div)

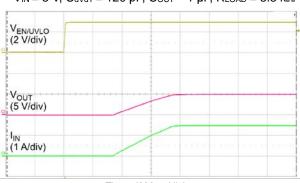

#### Over voltage clamp

The above characteristics curves are presented for reference only and not guaranteed by production test, unless otherwise noted.

Time t (200 µs/div)

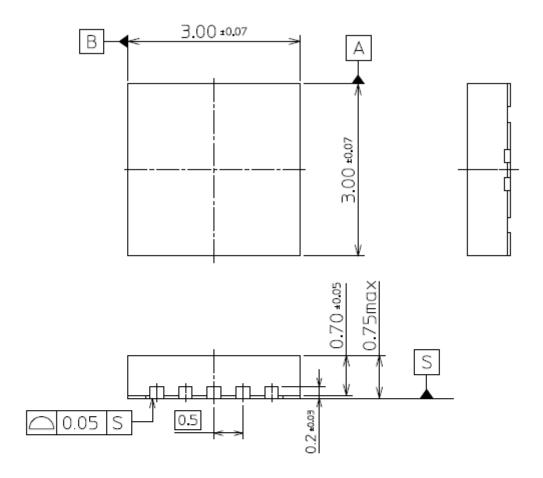

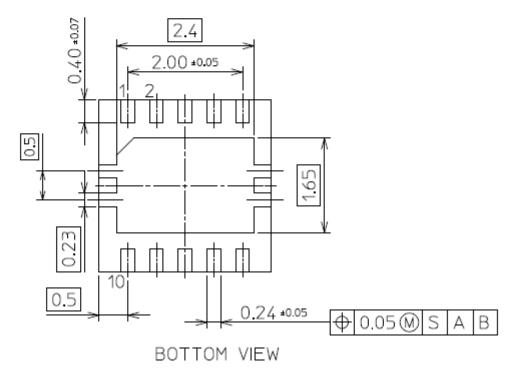

# **Package Dimensions**

WSON10B Unit: mm

Weight: 19.3 mg (typ.)

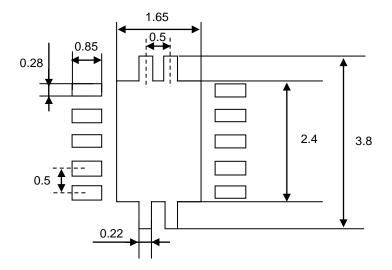

# Land pattern dimensions for reference only

Unit: mm

#### **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE

EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH

MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT

("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without

limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting medical

equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to

control combustions or explosions, safety devices, elevators and escalators, and devices related to power plant. IF YOU USE

PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your

TOSHIBA sales representative or contact us via our website.

- · Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE

FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY

WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR

LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND

LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO

SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without

limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile

technology products (mass destruction weapons). Product and related software and technology may be controlled under the

applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the

U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited

except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product.

Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES

OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

### Toshiba Electronic Devices & Storage Corporation

https://toshiba.semicon-storage.com/